技术博客 I 稳定电源转换的纹波降低技术

本文要点:

纹波在电源上表现为噪声。

要想提供稳定的电源,需要降低输出电压的纹波。

降低纹波的技术包括滤波和反馈精确调节。

所有的电源都具有一定程度的波纹,在设备输出口上表现为噪声。尤其是在开关 DC-DC 转换器的输出上,纹波是一个烦人的噪声问题。在一些应用中,特别是接收直流电源电压的模拟器件,需要有非常“干净”的电源,否则噪声可能会传播到器件的输出端。相比之下,饱和逻辑(例如 TTL 和 CMOS)抵抗此类噪声的能力更强。

采用开关调节的 DC-DC 转换器至少需要实施一种纹波降低技术,但该技术需要与适当的开关频率、功率输出和负载工作频率相匹配。负载阻抗也会对确定开关转换器的行为和实施的纹波降低技术的有效性有影响。本文将简要介绍几种纹波降低技术,以及它们在新型电源设计中的最佳应用场合。

纹波降低技术:简易版与高级版

纹波降低技术:简易版与高级版

纹波降低技术可以通过无源电路或有源电路,以及线性或非线性器件来实施。实施主动控制策略的一些算法试图补偿 DC-DC 转换器输出的波纹,其过程可能有点复杂,最好利用专用的 ASIC 来实施。

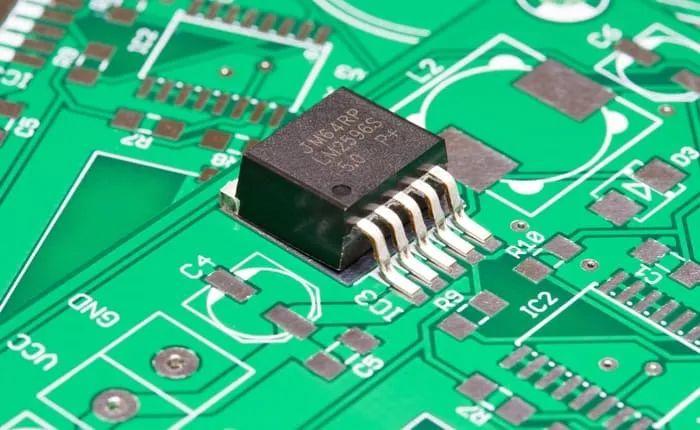

利用 LDO 进行调节

这种策略是一种入门级的纹波降低技术,适用于使用直流电源的器件。许多数字器件包含一个用于降低纹波的片上低压差 (LDO) 线性稳压器,提供的纹波降低效果可以达到 80dB 左右,这意味着纹波可以降低 1 亿倍!这类设计的原理是在器件中使用一个比较器和一个稳定的硅带隙参考电压源,使输出电压饱和。然而,该方法是通过饱和来降低噪声,因此当输入电压差和输出功率过高时,器件会产生大量的热量。

线性稳压器可以大幅降低纹波

滤波

用低通滤波器或陷波滤波器进行过滤,是解决纹波频率问题的一种策略。这种方法在直流稳压器中效果较好,特别是在实施滤波的时候。在 pi型(LC 电路)中实现的简单高阶无源滤波,可以在传递函数中提供很高的滚降系数,但需要非常大的电感和电容来滤除典型的 PWM 频率。一个更复杂的策略是使用有源滤波技术,将电抗添加到反馈环路中,这种方法可以提供非常高的直流增益并抑制交流输出。

反馈控制

反馈环路隐含在一些高度集成的开关稳压器器件中,特别是那些在同一封装中实现 PWM 振荡器、栅极驱动器和 FET 级的器件。对于在非常高的功率输出下运行的更先进的设计,需要一组分立器件来实现反馈回路的控制策略。一旦输出上的波纹可以与直流输出一起被感知到,能够调整 PWM 驱动信号和驱动频率的控制策略可以同时稳定输出水平和波纹。电源系统设计师们对这个领域进行了积极的研究。

较大的电感器和较高的 PWM 频率

这两种方法应该同时提及,因为它们是用于设置开关稳压器中初始纹波值的标准工具(在标准降压、升压和降压-升压设计中)。纹波水平与输出电感和 PWM 频率成反比,因此增加这两者将降低输出口上测得的纹波。

在较低的开关频率下,需要使用大型电感器才能达到目标纹波值。

多相调节

多相转换器实现了多个并联的开关级,但在相位上是彼此分开的。虽然这些电路可能要复杂得多,但它们的作用类似于单级稳压器,具有更大的开关频率和电感器。其结果是大大降低了输出端测得的纹波。只要输出过滤级的截止频率高于基带频率,这些稳压器就可以用于直流负载或调频信号的高频交流负载。这些转换器还可以提供高电流,同时不会对器件造成过大的压力,因为开关负载被分散到多个开关级上。

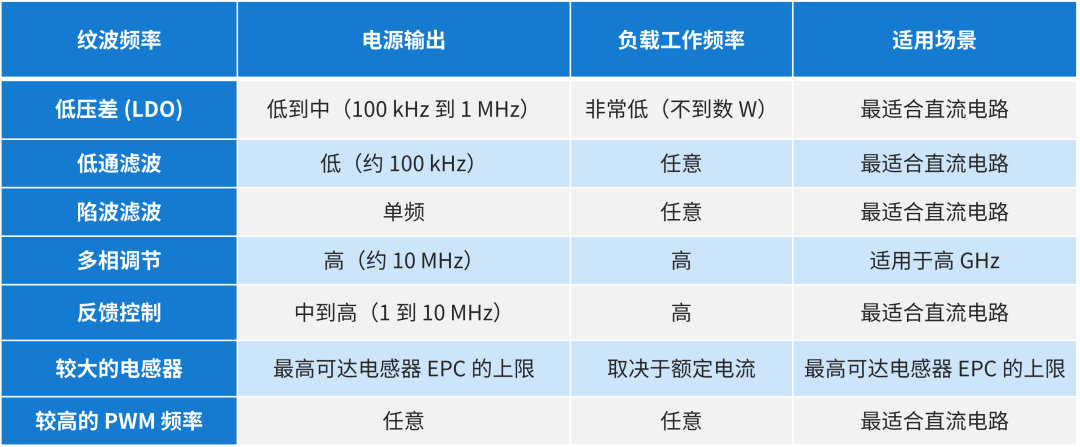

纹波降低技术总结

纹波降低技术总结

下表说明了各种纹波降低技术在哪种情况下适合用于开关式 DC-DC 转换器。设计师应该注意使用各个方法来实现纹波降低,因为如果在错误的情况下使用,相应的机制可能会失效。

点击查看大图

最后要考虑的一点是,这些方法在新的设计中往往是一起实施的。例如,用于射频电源系统和大功率射频发射器的降压转换器可以使用高阶低通滤波、多相调节和高 PWM 频率(几 MHz 或更高),并在反馈回路中采用无源或有源控制方法。选择正确的技术组合需要考虑各个因素,从负载的行为到转换器级的操作。要评估这些设计,可以从带有高精度器件模型的 SPICE 仿真开始入手。