技术博客 I 天线的阻抗匹配技术

本文要点

天线的阻抗匹配技术旨在确保将最大功率传输到天线中,从而使天线元件能够强烈辐射。

天线阻抗匹配是指将天线馈线末端的输入阻抗与馈线的特性阻抗相匹配。

为此通常会使用滤波电路,因为经过配置之后,它们可以在所需传输频率上提供特定阻抗。

虽然天线的形状和尺寸多种多样,但它们有一个共同点:需要在馈线末端施加阻抗匹配,以确保向负载传输最大功率。阻抗匹配电路非常简单;它们充当滤波器,可确保天线的馈线阻抗与天线输入端口的输入阻抗相匹配。要在天线或其他 RF 电路元件实现阻抗匹配,最简单的方法是从滤波的角度出发。

1

定义阻抗匹配要求

定义阻抗匹配要求

天线阻抗并不总是 50 欧姆,因此需要运用阻抗匹配技术。有些天线(如芯片天线)在制造时阻抗较低或较高。对于其他天线,如印刷天线,可能很难设计出完全符合 50 欧姆目标阻抗的天线;走线可能非常宽,或者天线可能占用电路板空间。最终的结果是需要缩小天线尺寸,因而造成阻抗失配。

此外,天线及其匹配网络可能连接到短馈线,因此馈线的输入阻抗可能不等于馈线的特性阻抗。相反,输入阻抗需要与发射器的输出阻抗相匹配,以便尽可能降低天线输入端和馈线输入端的回波损耗 (S11)。虽然带有集成式 RF 收发器的设备通常采用或可以配置 50 欧姆的片上终端 (on-die termination),但这并不意味着阻抗匹配是完美的。

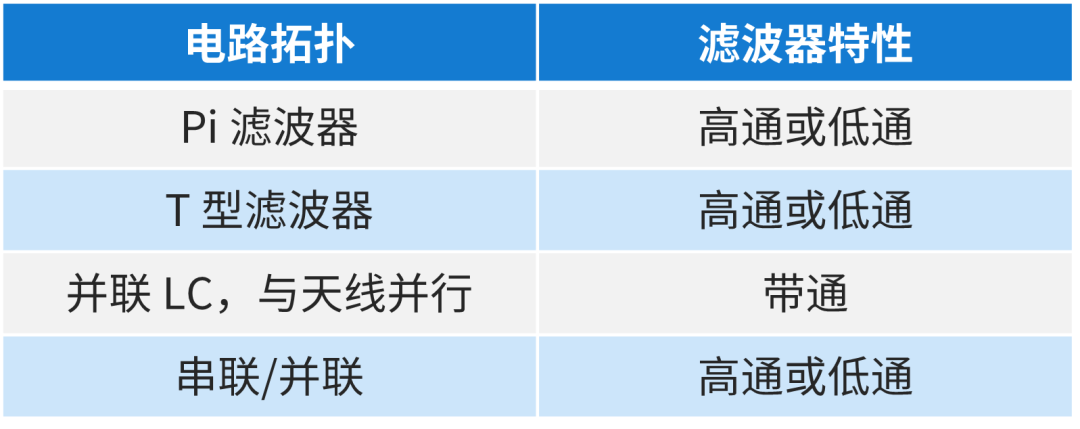

如果采用基于电路的方法,天线阻抗匹配技术有多种选择。目标是确保(天线 + 阻抗匹配网络)等效阻抗与传输线入口处的输入阻抗相匹配。典型的电路拓扑结构如下表所示:

串联 LC 滤波器之类的电路没有用处,因为它们会有一个阻带。如果需要达到非常快速的滚降,也可以使用高阶 RF 滤波器,不过这会增加元件数量。无论使用哪种类型的滤波器来实现阻抗匹配,(天线 + 阻抗匹配网络)阻抗都应与天线馈线特性阻抗相匹配。为此,可以通过 SPICE 仿真进行评估。一旦确定了这种匹配,就可以回溯到天线输入端口,确保进一步匹配。

输入阻抗

(天线 + 阻抗匹配网络)与馈线的目标阻抗相匹配后,下一步是确保输入阻抗也与 50 欧姆相匹配。利用天线输入端的反射系数和标准传输线输入阻抗方程,就可以很轻松地做到这一点:

已知传播常数和所选长度的馈线输入阻抗。请注意,在计算馈线的输入阻抗之前,必须先知道天线的阻抗。

理想情况下,天线阻抗也应达到 50 欧姆。然后可以计算馈线输入端的 S11(回波损耗);典型的设计目标是该输入端口的损耗不超过 20 dB。

Stub 匹配

传输线 stub 也可以作为并联元件,就像并联电容器或电感器一样。只需将上述输入阻抗方程用于 stub 部分,即可计算出 stub 充当等效电路元件的作用。在使用印刷电路元件的无源 RF 电路中,stub 的使用非常普遍,因此也适合用于实现阻抗匹配。请注意,由于电磁场在传输线 stub 上的传播行为,可以使用开路或短路传输线 stub 来匹配多个频率。

2

阻抗匹配电路的替代方案

阻抗匹配电路的替代方案

在本文中,我们研究了使用各种滤波电路进行阻抗匹配的方法,在连接芯片天线、同轴连接器,甚至印刷天线、走线或缝隙天线时,这些方法十分常见。电路设计方法是标准方法,因为在 SPICE 仿真器中实施参数扫描非常简单,可检查天线输入端口的输入阻抗和反射系数。对于不喜欢使用电路仿真的用户,也可以使用其他工具来实现天线阻抗匹配。

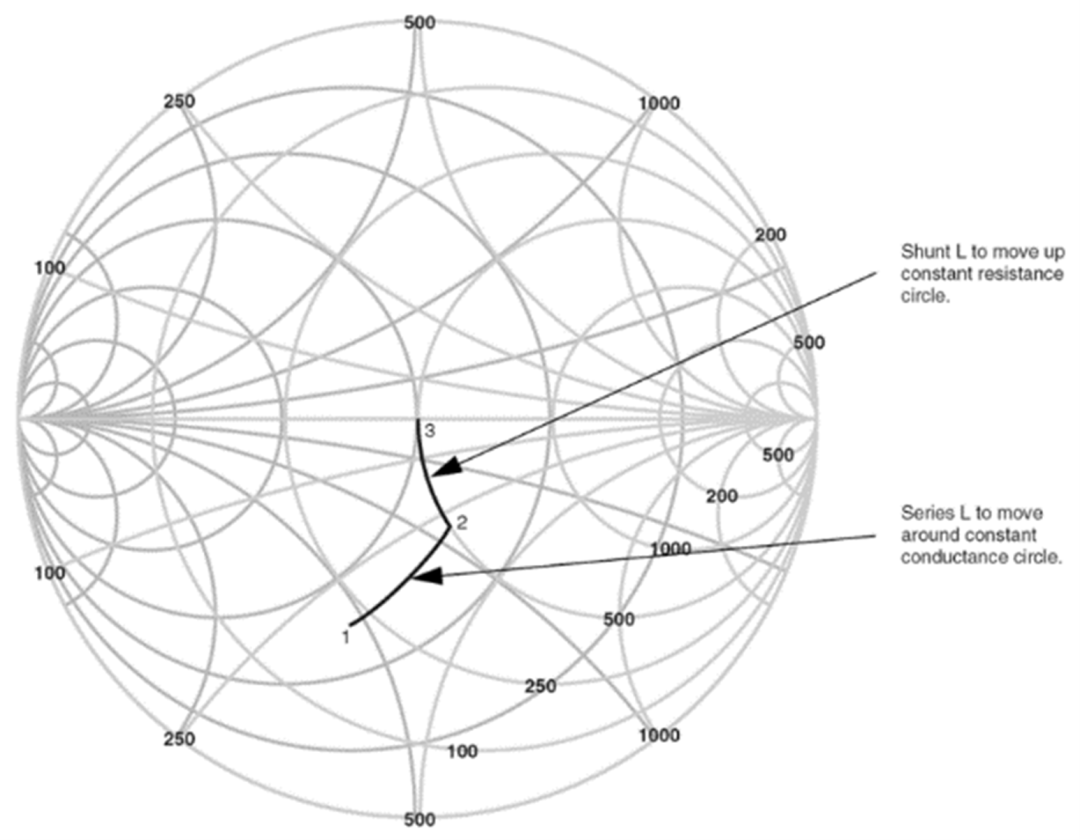

史密斯圆图也可以用于实现天线阻抗匹配。这是一种应用阻抗匹配的图形方法,需要添加串联或并联的 L 和 C 元件来跟踪(天线 + 匹配网络)组合的阻抗。网上有许多关于如何使用史密斯圆图的指南,我们建议新手天线设计人员在首次尝试使用史密斯圆图时先参考这些指南。请务必牢记在图表中应用 L 和 C 元件的串联和并联规则(见下文)。

史密斯圆图的串联和并联规则用于将(天线 + 匹配网络)的总阻抗移至 50 欧姆的目标阻抗。

针对非标准辐射体的最后一种方法是使用电磁场求解器。3D 有限差分频域 (Finite-difference frequency domain ,即 FDFD) 仿真可用于检查设备发出的电磁场,然后将其与天线中的电压和电流分布相关联。更复杂的求解器可以从这些结构中提取网络参数,直接计算输入端口和所需发射频率/带宽的 S11。然后,设计人员就可以利用这些数据,使用上文概述的其他技术来确定天线设计的阻抗匹配量。