DIE电容的测量

本文介绍几种使用VNA两端口测试方法测量DIE上电容。

分别测量如下三种情况下的DIE电容:

1)在DIE的bump位置观测;

2)在pkg的ball的一个pair位置观测;

3)在pkg的ball的两个pair位置观测

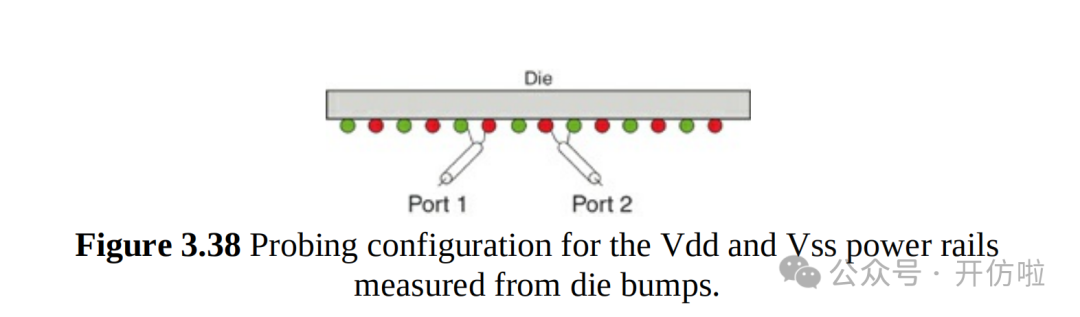

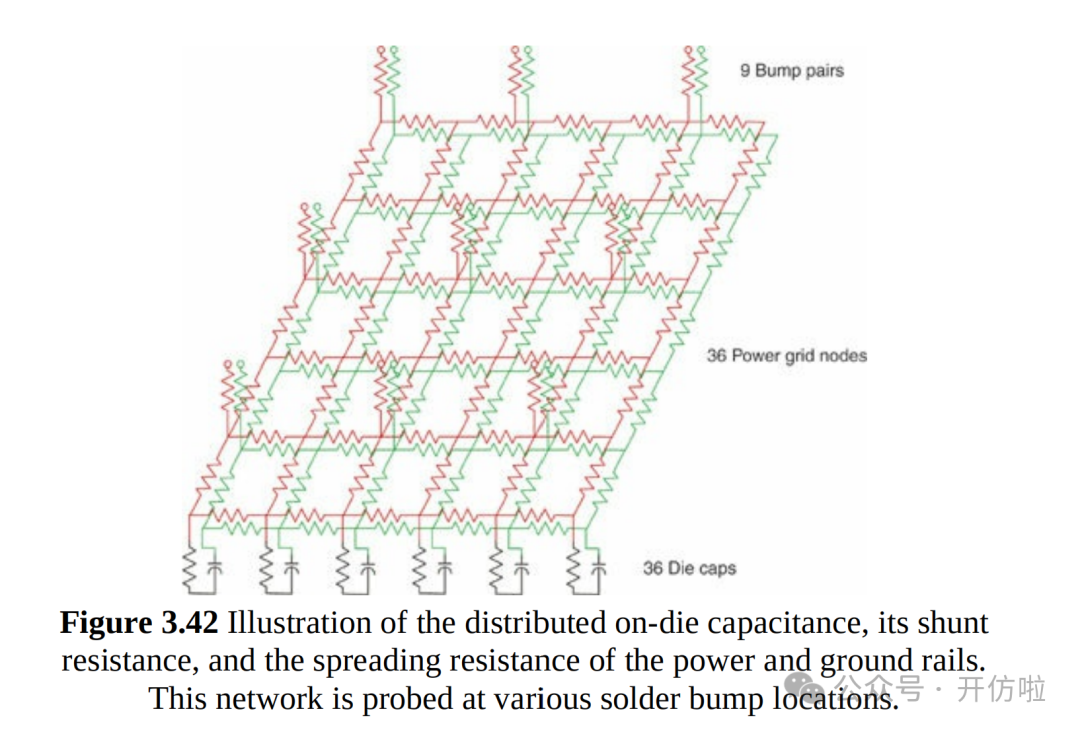

第一种测试结构如下:

其中VNA校准到微探头的探针位置,探针位置不能准确校准的位置使用50ohm、1ps传输线代替。

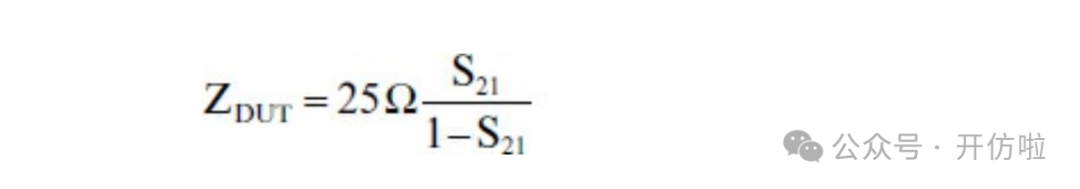

VNA测试从300KHz到3GHz,测试S21,通过以下公式转化为阻抗参数:

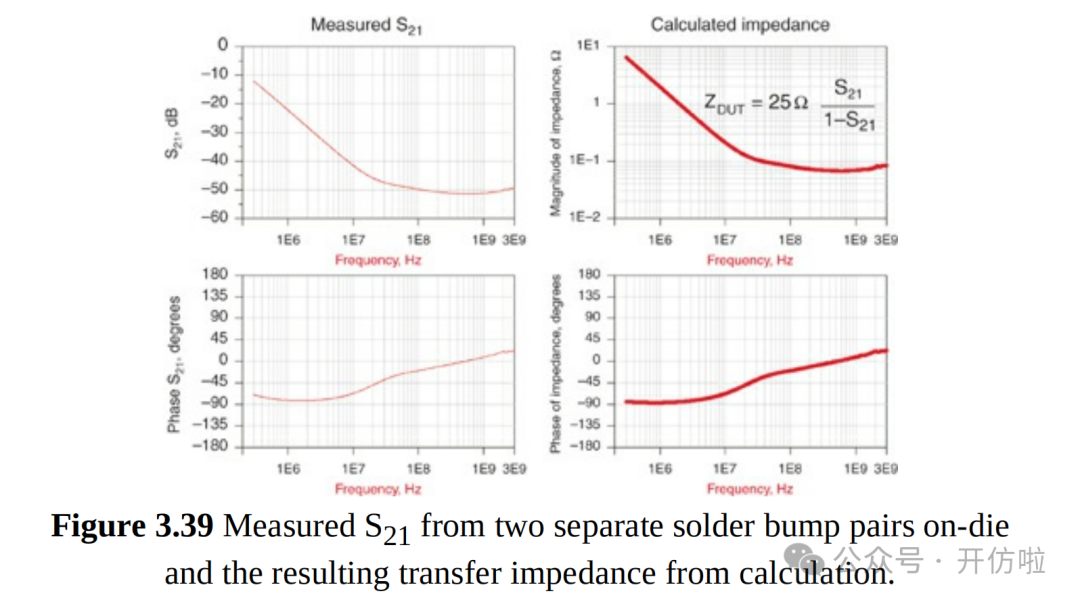

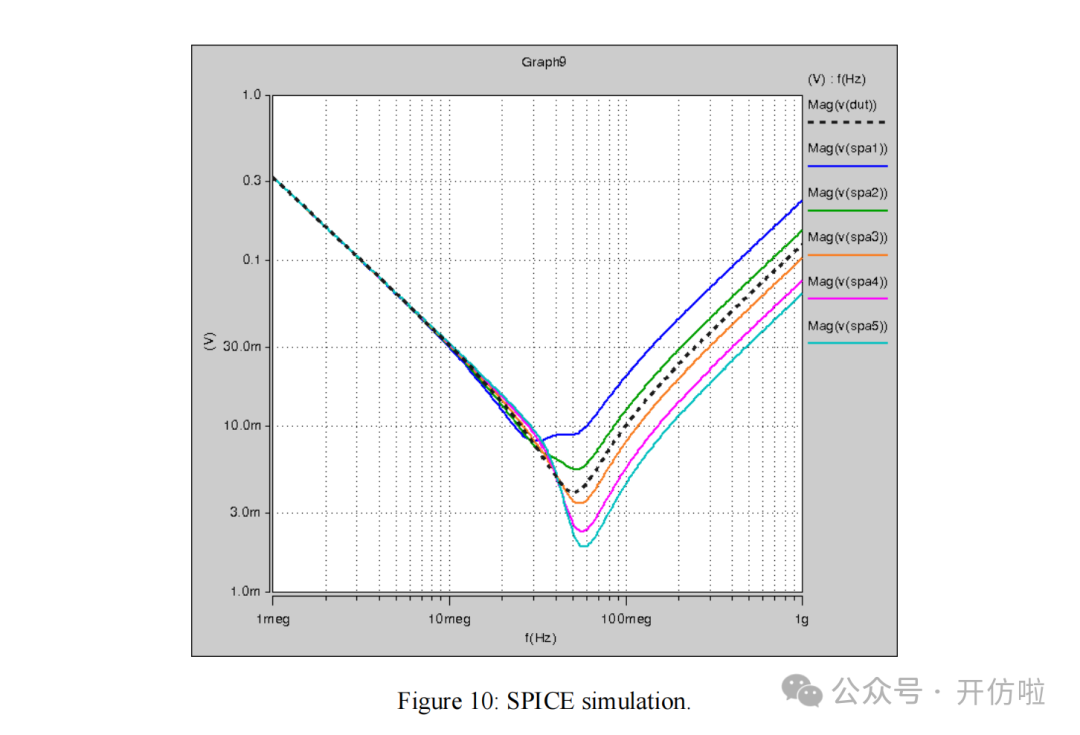

使用RLC电路搭建仿真模型,结果对比如下:

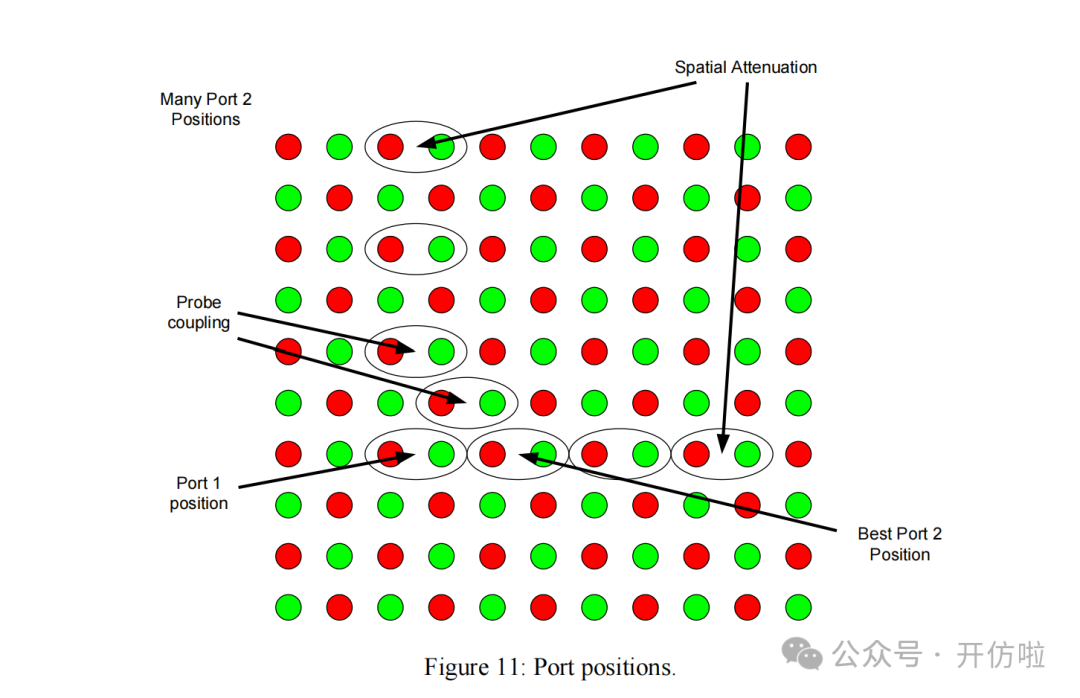

但是需要注意,在测试时,根据DIE位置的RLC网络参数分布,两个端口距离越远,S21(或者转移阻抗)会减小,因此计算出来的阻抗也越低,但是是不准确的,因此,两个port不能离太远;但是也不能太近,太近则会有磁场互相串扰,产生互感,因此需要适当权衡。

这种现象在PCB上测试时,会更明显。

------------------------------------------------------------------------

插播一下:

参考论文[Larry D Smith_2011 DesignCon - On Die Capacitance Measurements in the Frequency and Time Domains]

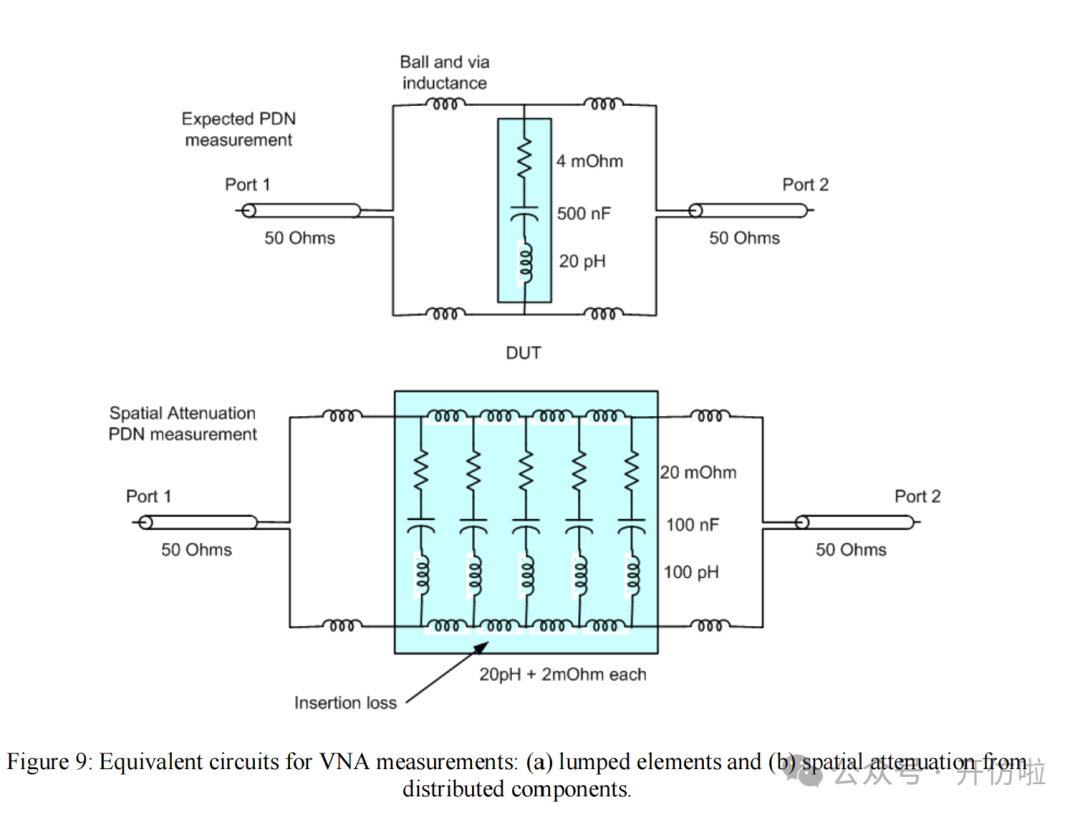

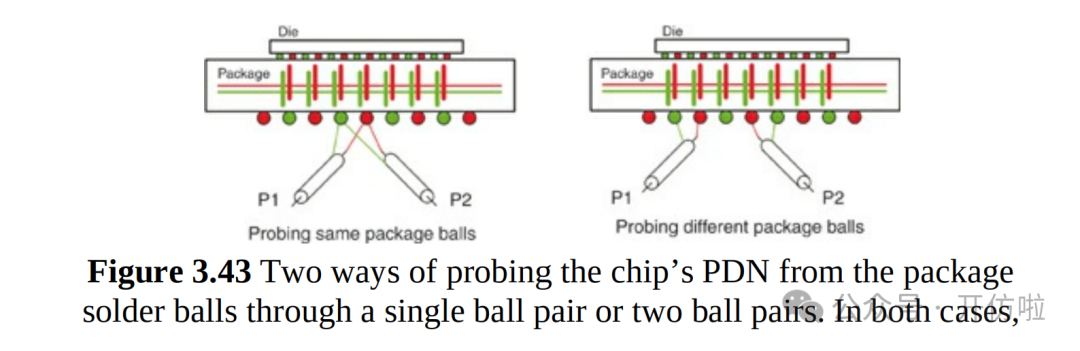

其中对于两个端口的距离进行了实测研究,测试示意图如下:

测试结果如下:

推荐的测试端口位置如下:

------------------------------------------------------------------------

下面接着看一下在ball位置测量阻抗的结构,如下:

第一种测试方法,pkg的ball和via电感都被算到DUT阻抗里了;

第二种测试方法,pkg中的一部分(从pkg的plane开始,两个探测点第一次接触),算入DUT阻抗中;

因此,第二种更准确。

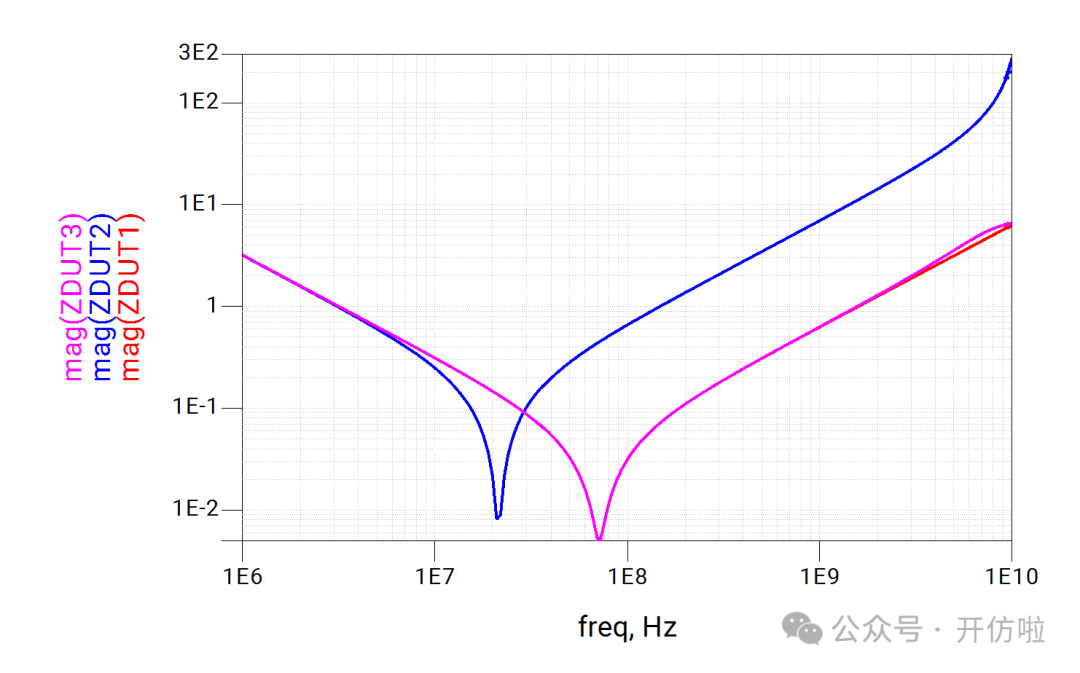

做了一个仿真对比:

红色曲线为不带夹具传输线模型时,DUT的阻抗,粉色为带传输线模型时的DUT阻抗曲线,蓝色为两个port在同一个位置而引入了一部分电感或者传输线在DUT中时的阻抗曲线;

可以明确确认将其他部分串联进DUT时,电感会直接影响DUT阻抗(两个port在同一位置测试时),而两个port在两个位置时,则只会在高频部分影响测试精度,而不会将每个port部分的独立电感串入DUT中;

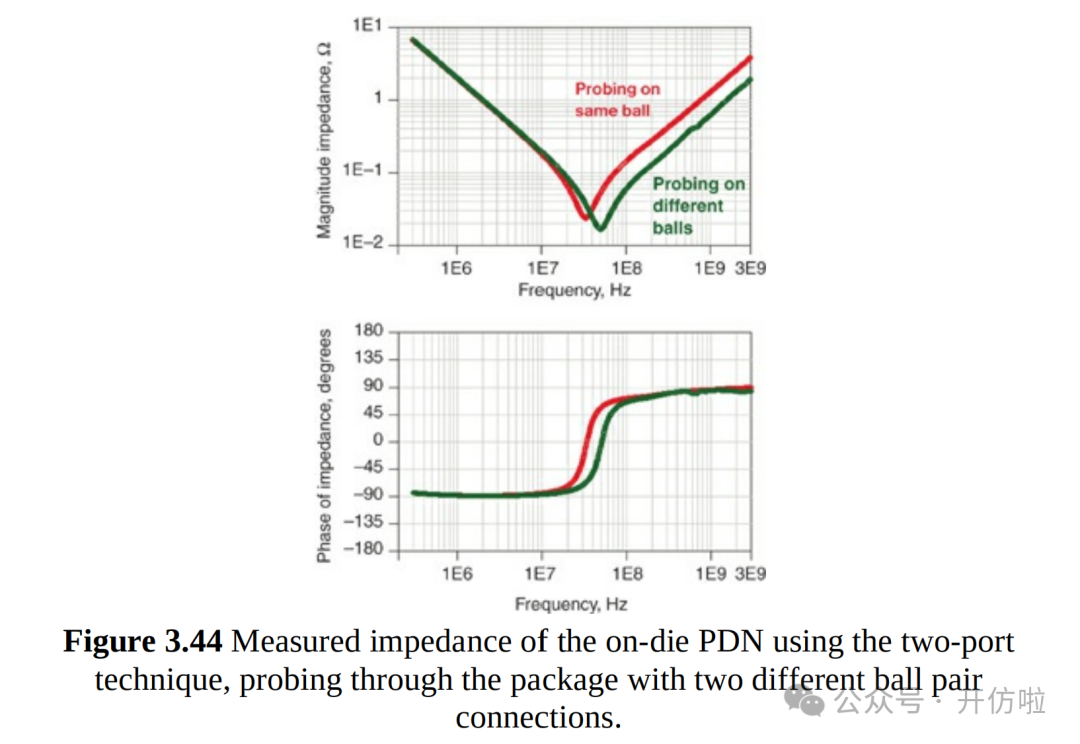

对于这两种测试结构的测试结果如下:

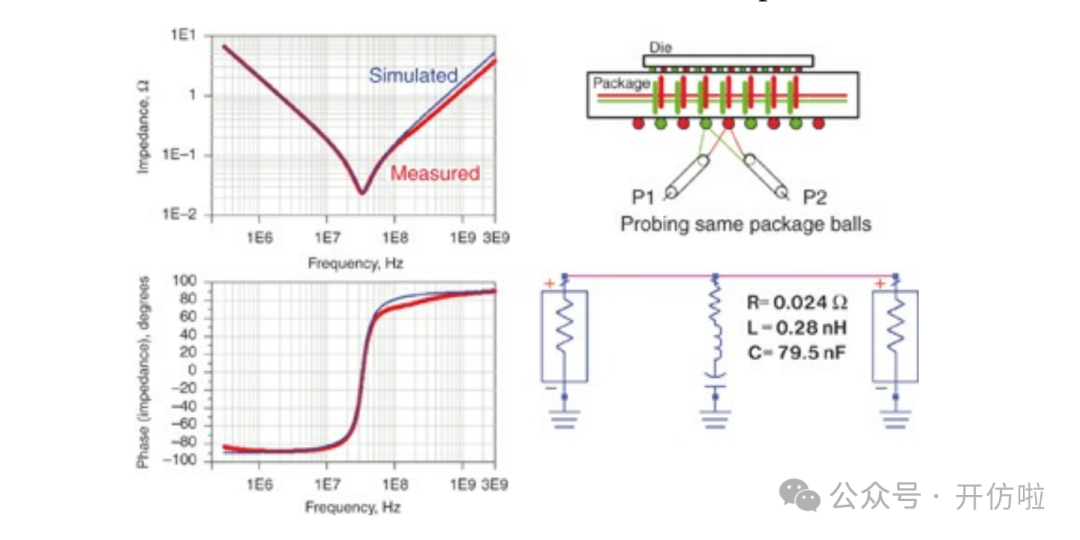

用RLC电路仿真阻抗,与两个port在同一位置的测试阻抗曲线对比如下:

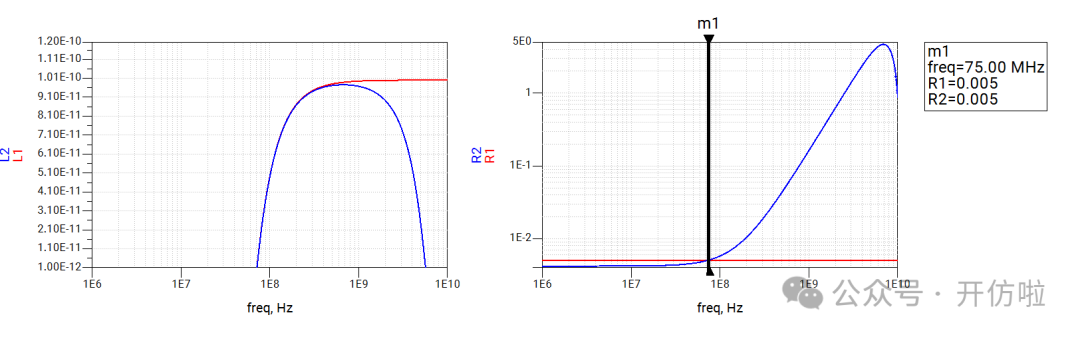

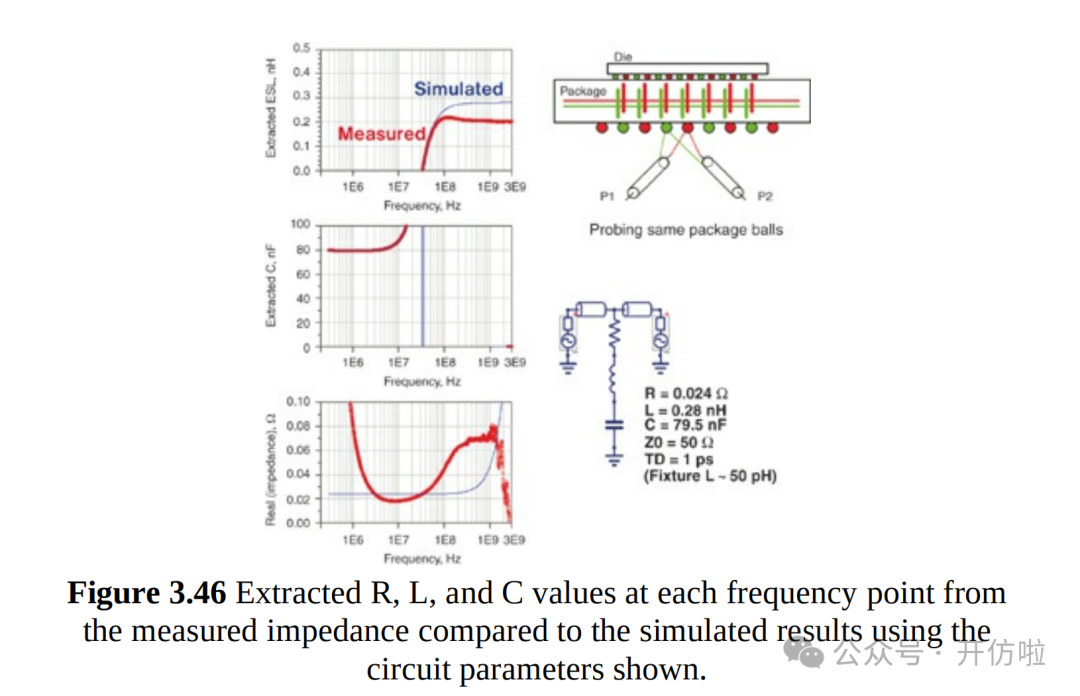

将其分解为R和L,如下:

可以看到,夹具在这里的影响比较小,有一些影响是来自DIE的结构。

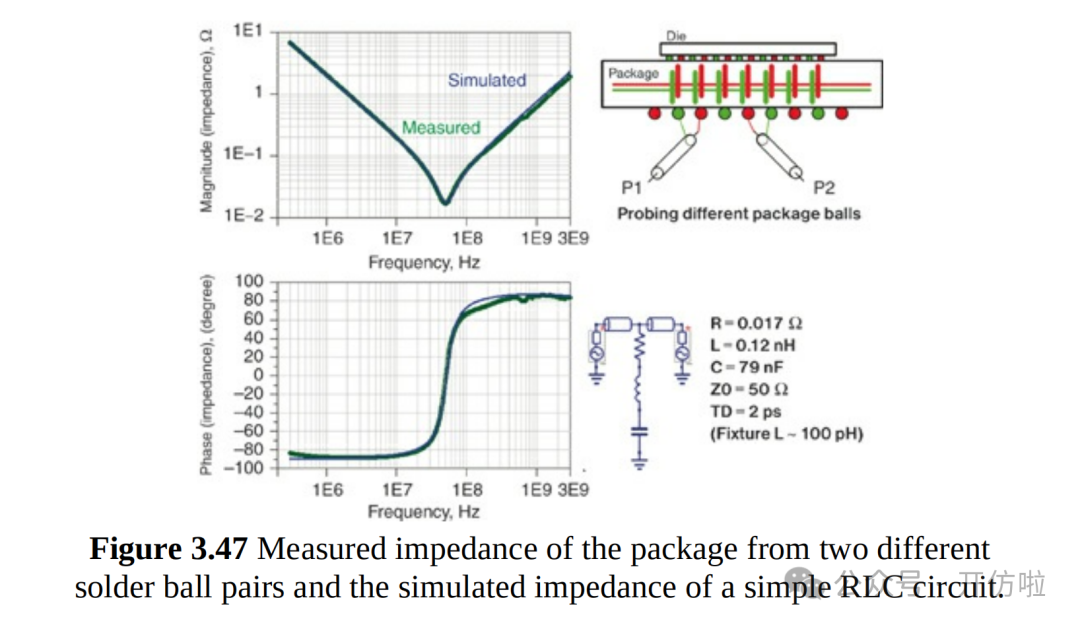

第二种测试结果如下:

无论哪种方法,低频阻抗都是取决于DIE电容,自谐振频点取决于DIE电容和等效电感,两个port在同一ball位置时,等效电感为0.28nH,两个port在两个ball位置时,等效电感为0.12nH;

这个0.16nH的差别主要是pkg的ball、via、以及plane的电感;

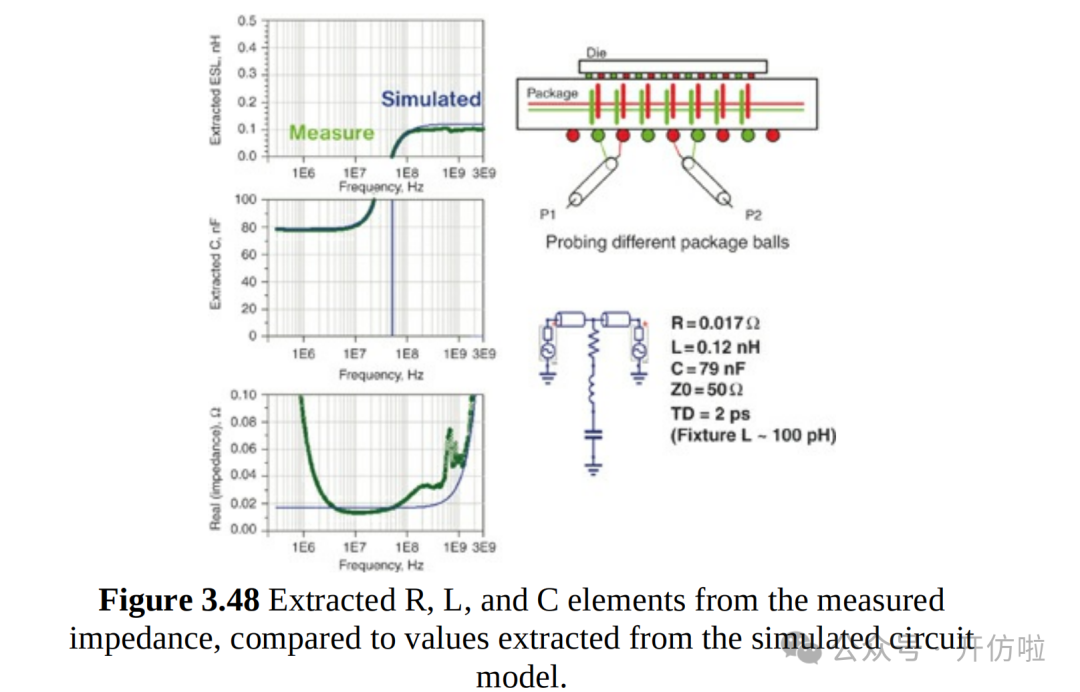

将阻抗参数分解为R和L参数如下:

电感参数仿测结果基本一致,且并不随频率变化;

电阻的测试值表现出了随频率的变化,与仿真结果不同,说明此处并非夹具引起的,而是DIE结构的低电感、高电阻特性引起的;

在100MHz范围内,典型的DIE电容和pkg电感的并联谐振点会出现,此时环路中的ESR主要是来自pkg的小电阻;在高于500MHz时,ESR主要来自于DIE上分布的电阻(比pkg上的大);

在DIE位置观测的高于1GHz的阻抗只能在3D模型中提取才准确,包括DIE上的大电阻、小电感,与pkg上的小电阻、大电感的并联电路。