《数字电子技术》之第三章 逻辑门电路

对于数字电路设计而言,HDL编程很重要。这是FPGA设计师所必备的知识!到企业上过班的人都知道这一点,所以在本文我不得不多讲讲这方面的知识,然后再讲解第三章的内容。

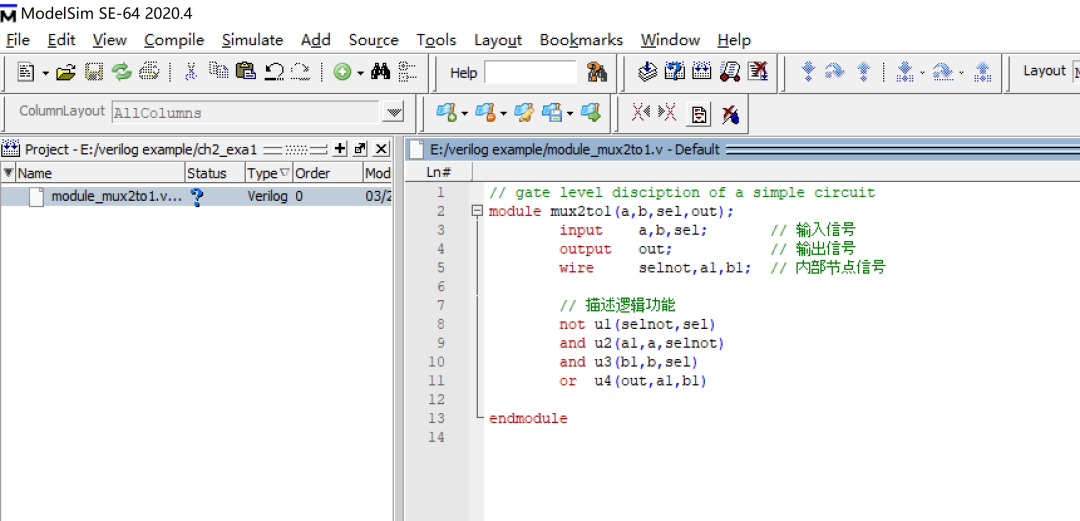

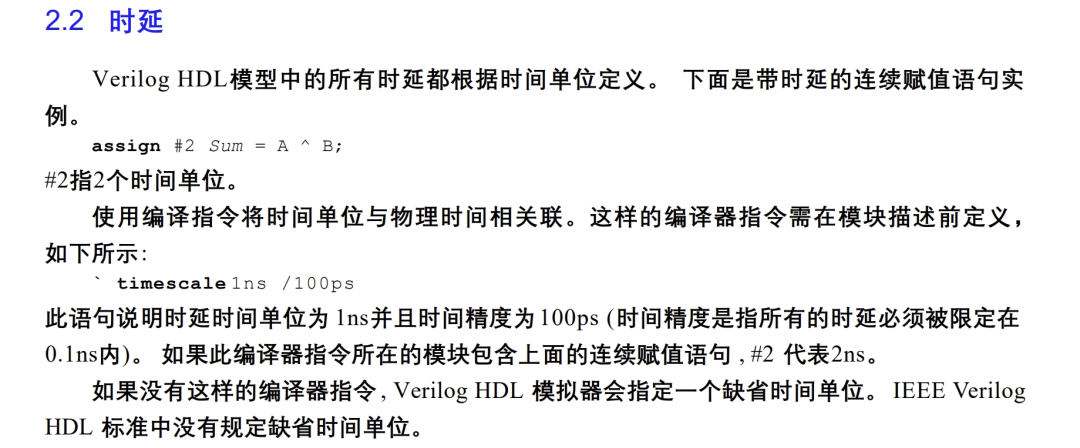

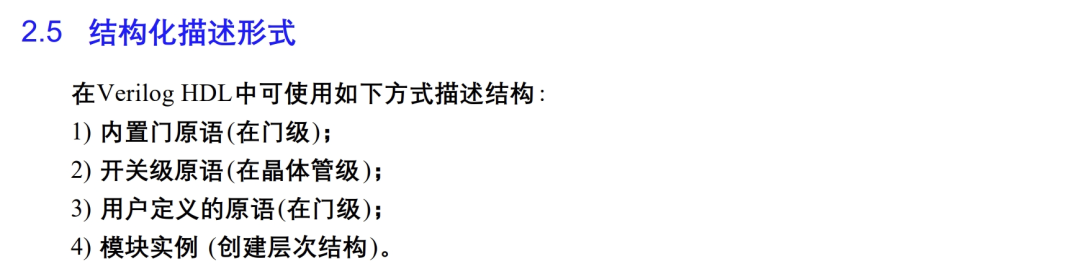

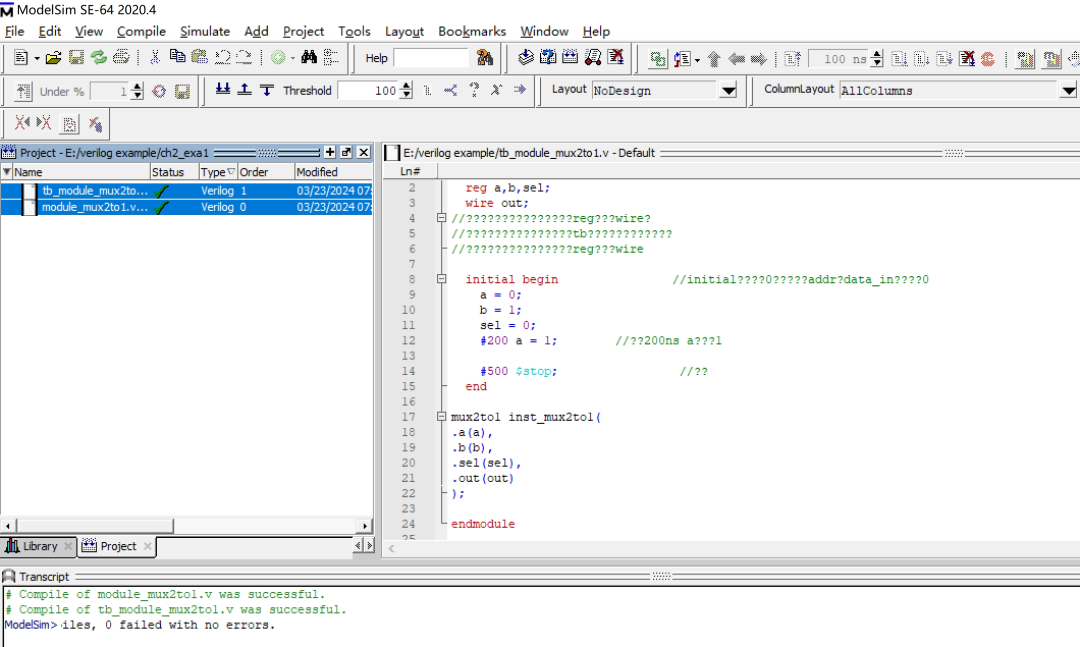

当年我也学过一些,后来专注算法研究,不过有了这些基础,和FPGA设计人员交流会很方便。至今还记得和前同事老马一起奋力攻克HSP系列芯片的日子,无数个不眠之夜!厂子里等米下锅,压力都来到我这边,于是那三个月把我累的够呛!好在那时候我的领导也能抗事情,顶住压力只要求给我时间,坚信我能做出来产品!好在结局很圆满!只不过过程确实很辛苦!现在市面上有很多可以用来做FPGA开发的软件,如Vivado、Quartus和Modelsim,但是这里向大家推荐使用Modelsim是因为大家现在要做的只是简单的一个数电知识的Verilog实现和仿真,所以用不到很多功能,而且一个Vivado装完就要上百个G,这对电脑的配置要求不低,而Modelsim占用空间不大,用起来也方便,仿真速度快,能让同学们感受知识实用的过程!即使是在用Vivado进行大型项目的开发,也经常关联Modelsim用它进行仿真。系统的学习理论知识一定要看书,这是我在读研期间看的一本电子资料。现在给大家做简要介绍。说明部分用于定义不同的项,例如模块描述中使用的寄存器和参数。语句定义设计的功能和结构。说明部分和语句可以在模块中的任何地方。但是变量、寄存器、线网和参数等的说明部分必须在使用前出现。为了使模块描述清晰和具有良好的可读性 , 最好将所有的说明部分放在语句前。这里将教材第二章的模块内容写入文件,在公 众 号里面将教材的内容一一复现!从不懂到懂的过程充满了新鲜感,我喜欢这样的摸索过程。大家体会一次这样的过程,估计也会喜欢上。现在大二的小王同学就已经经历过这样的摸索,于是学的更加勤奋。等到了大家有了很深厚的理论基础,那就该享受探索过程了,在攻读博士阶段会感受到!我现在就和大二学生一样,都是初学者。我也按照书上的内容一步一步的做,遇到不会的就去百度找资料看!对于大二学生,如果培养了这样的学习习惯,那么会快速的学会很多知识点,而且还能提升独立学习的能力。请注意连续赋值语句是如何对电路的数据流行为建模的。这种建模方式是隐式而非显式的建模方式。此外 ,连续赋值语句是并发执行的,也就是说各语句的执行顺序与其在描述中出现的顺序无关。在模块中,结构的和行为的结构可以自由混合。也就是说,模块描述中可以包含实例化的门、模块实例化语句、连续赋值语句以及always语句和initial语句的混合。它们之间可以相互包含。来自always语句和initial语句(切记只有寄存器类型数据可以在这两种语句中赋值)的值能够驱动门或开关,而来自于门或连续赋值语句(只能驱动线网)的值能够反过来用于触发always语句和initial语句。现在大家可能明白了,之前第二章的例子是混合式描述方式,而教材中用的是结构化描述方式。教材中让我们加入测试信号,我们看看如何完成?看到这里大家可能明白了需要两个文件才能做仿真,之前教材给出的只是设计文件,还需要一个测试文件!Verilog HDL不仅提供描述设计的能力,而且提供对激励、控制、存储响应和设计验证的建模能力。激励和控制可用初始化语句产生。我们需要看怎么通过编写一个新的文件来产生测试信号也就是激励信号!在得到设计文件之后,如何验证我们的设计文件能否实现我们预想的功能?一般我们就需要进行仿真,仿真无疑就是希望它能工作起来,那此时我们就需要从设计的模块外部给他一个激励,让他能够运转起来。在设计文件中,我们有input、output,但是如果我们不给输入激励它完全是没法运转起来的。我们可以设计各种各样的激励文件,我们一般称之为testbench,想让输入怎么变他都可以怎么变,接下来对照上面的选择器,我们需要写一个激励文件testbench。写好了,看如何运行?需要先编译,编译通过后再进行仿真!

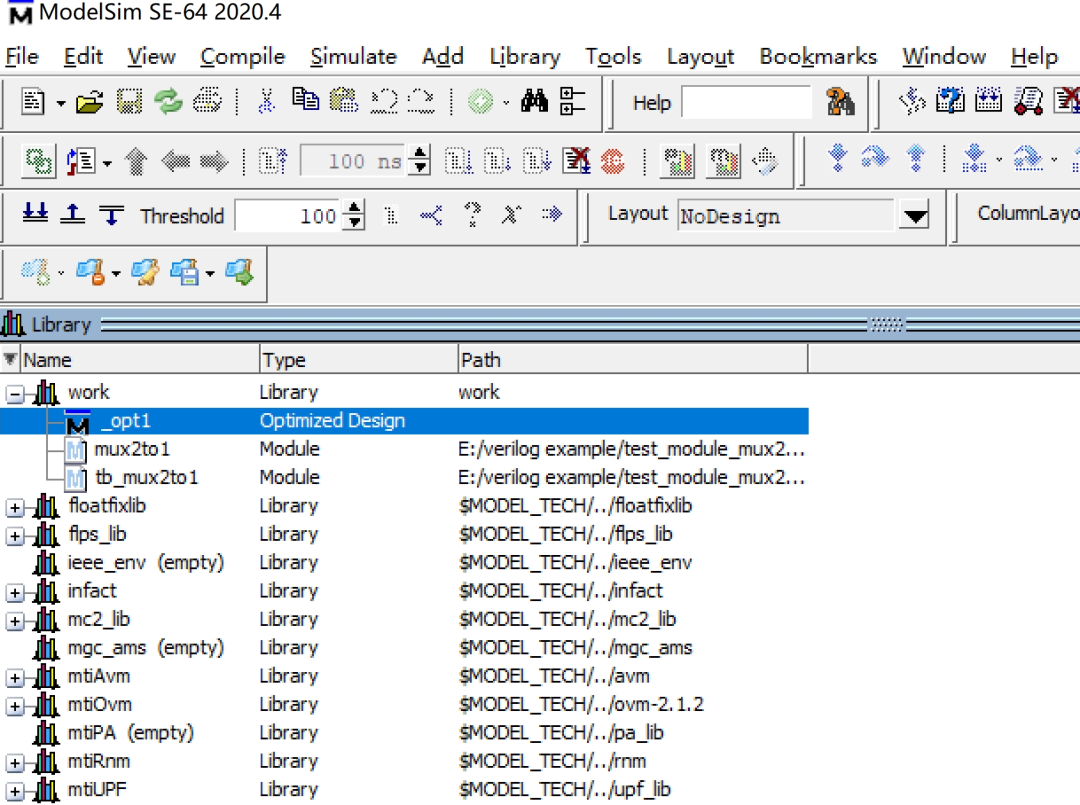

编译后,程序如果没有问题后会显示绿色的√,如果报错根据报错信息检查代码进行修改。查找错误吧!这里的激励文件是tb_module_mux2to1.v!!!

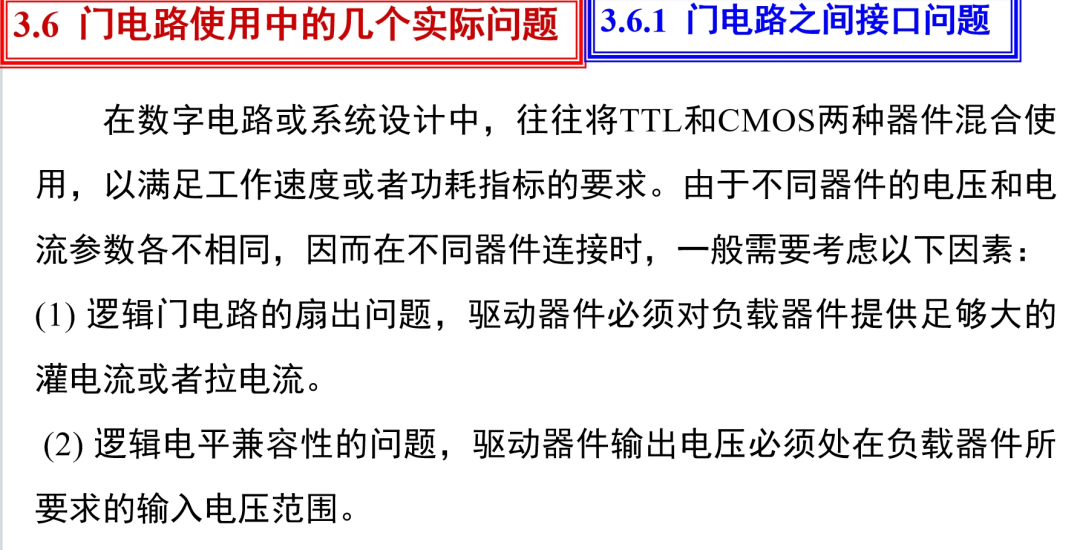

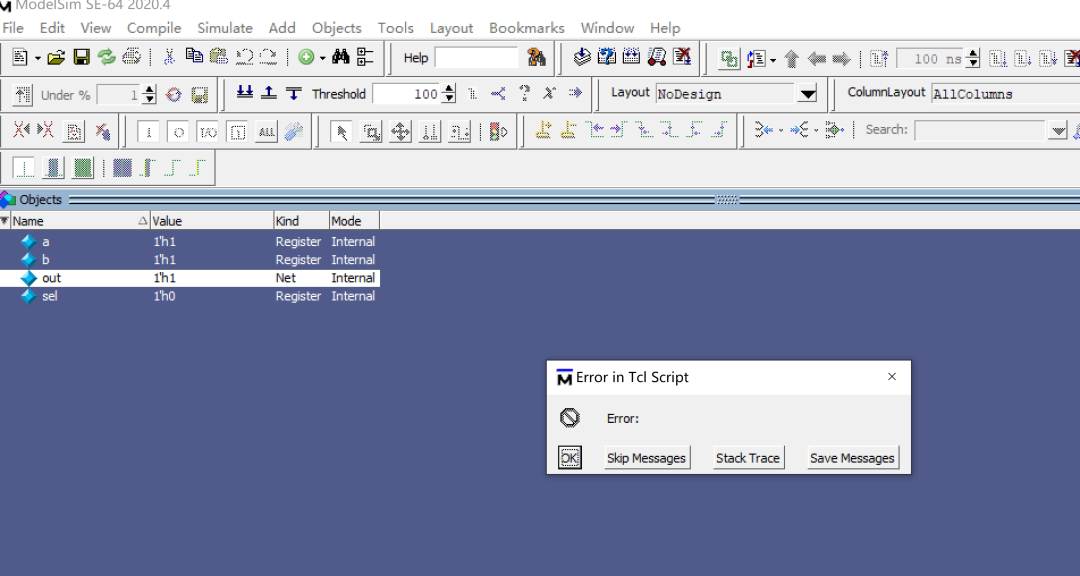

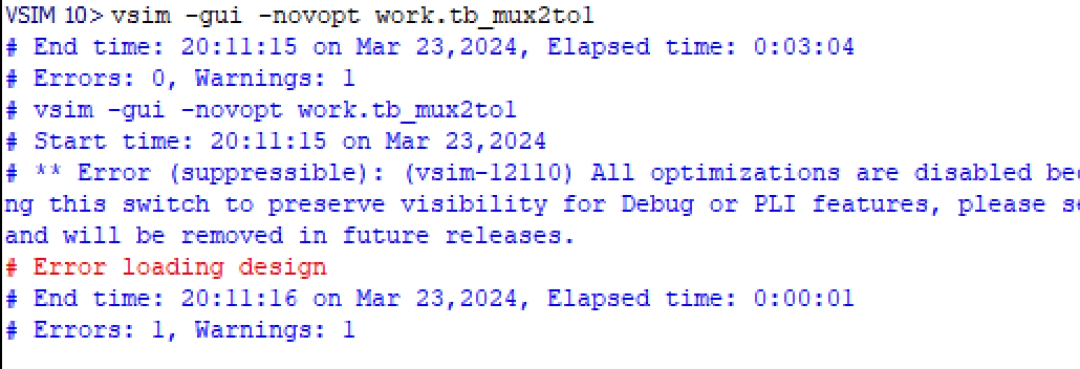

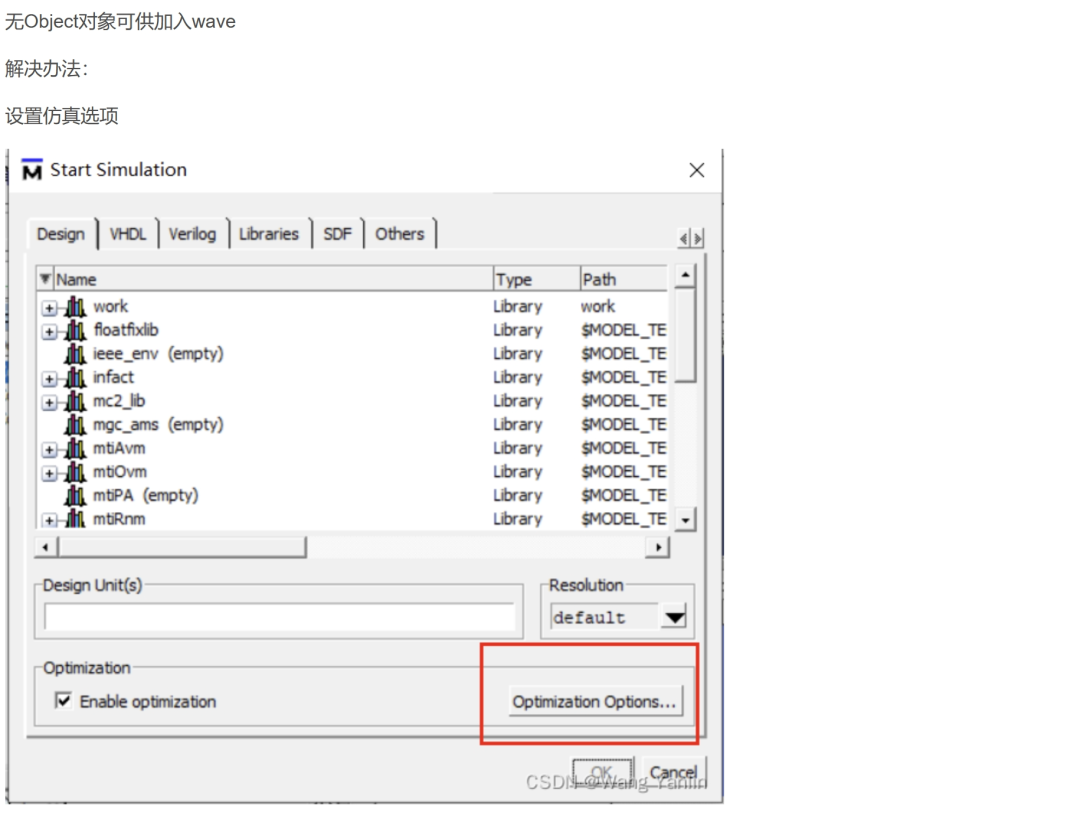

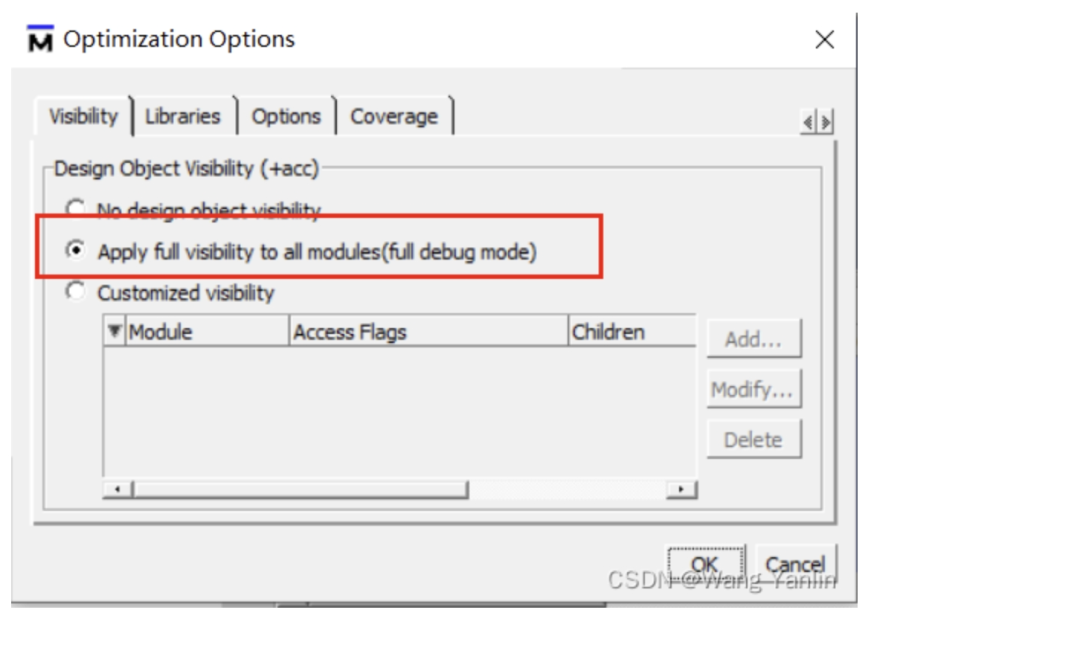

点击ok!但是仿真的时候看不到结果!于是加上模块例程!不知什么原因了,编译通过了,仿真出了问题!只有耐心在网络上找答案。毕竟这个问题都是非常基础的问题!按照这个修改后,仿真结果也出来了!之前尝试了多种方法,比如修改程序和去除优化选项等等,甚至还担心软件版本问题!全是白费力气!直到百度上这么搜索了!做了多个尝试,耗时两个小时!最后依旧是从互联网上找到了答案!纸上得来终觉浅!当年是趋势,现在则是主流!希望同学们能够把这部分内容在自己电脑上实现!看看老师的讲解过程,包含着各种错误修订和软件应用摸索过程!再来看看学生编写程序和调试程序的过程!加油,实践出真知!希望有更多的同学能够给老师和网友们展示编程过程,一起进步!进入第三章的学习!  拉电流:驱动门输出高电平时,从驱动门流出的电流,总拉电流和负载门的数量相关。灌电流:驱动门输出低电平时,从驱动门流出的电流,总灌电流和负载门的数量相关。

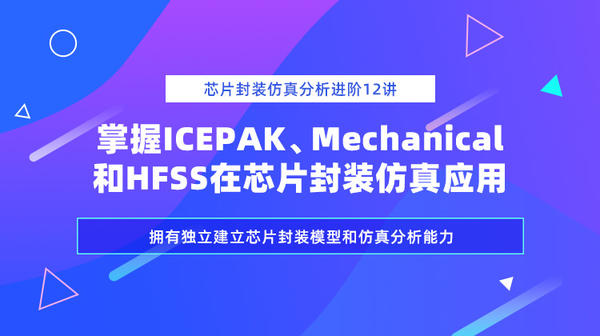

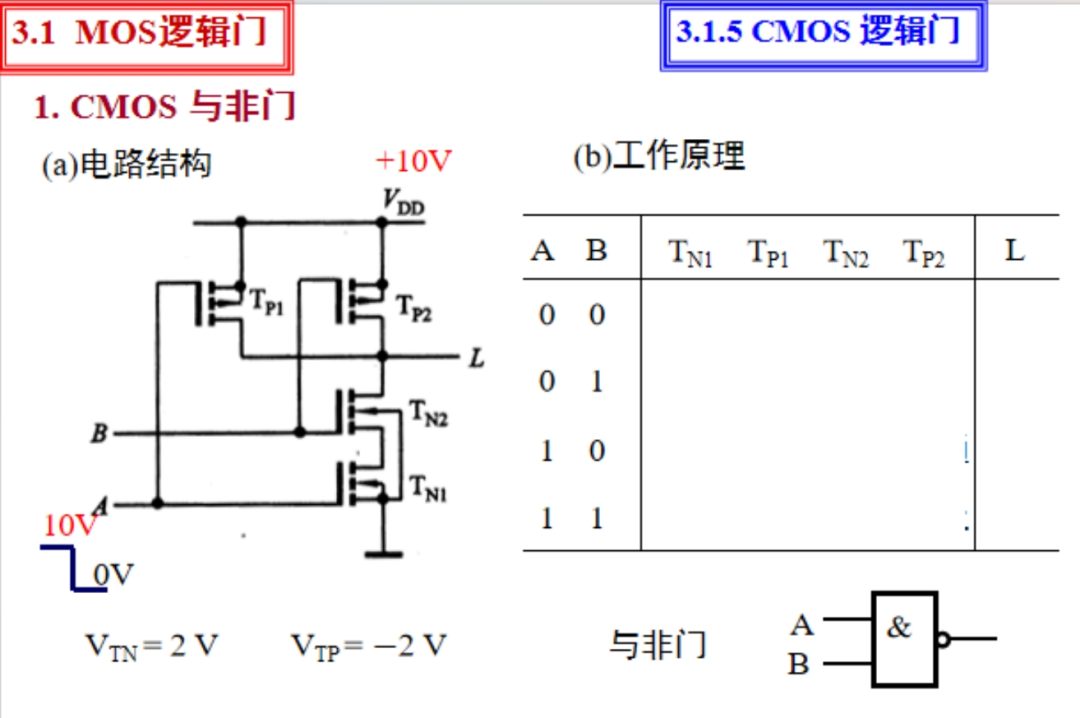

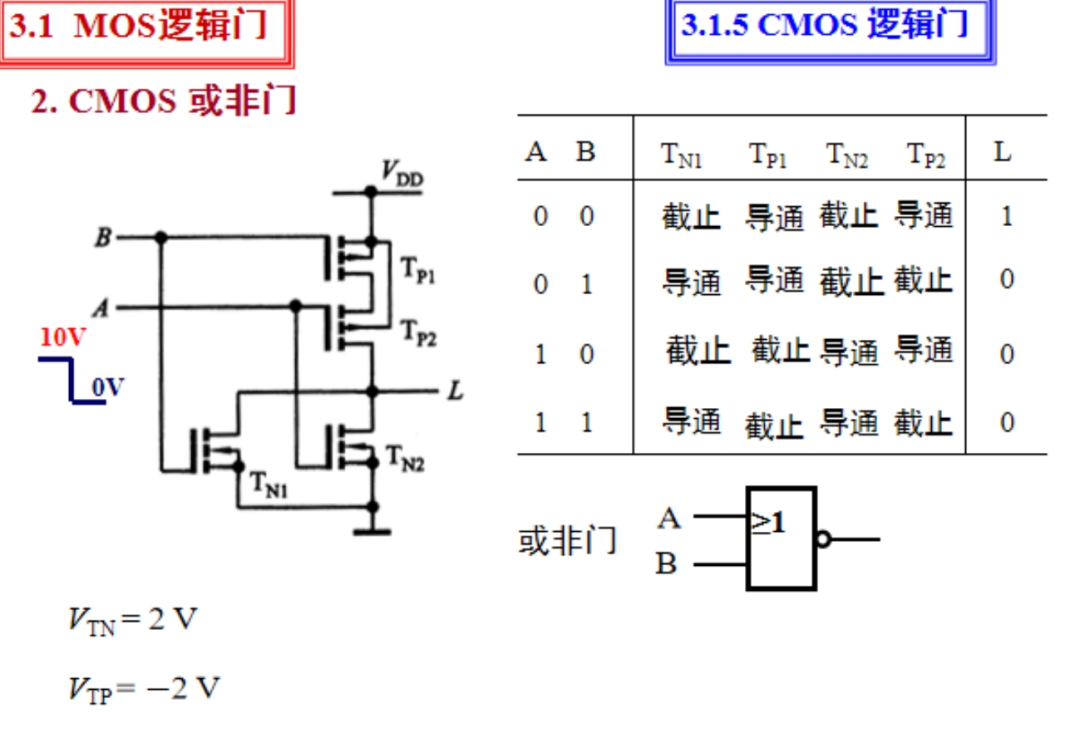

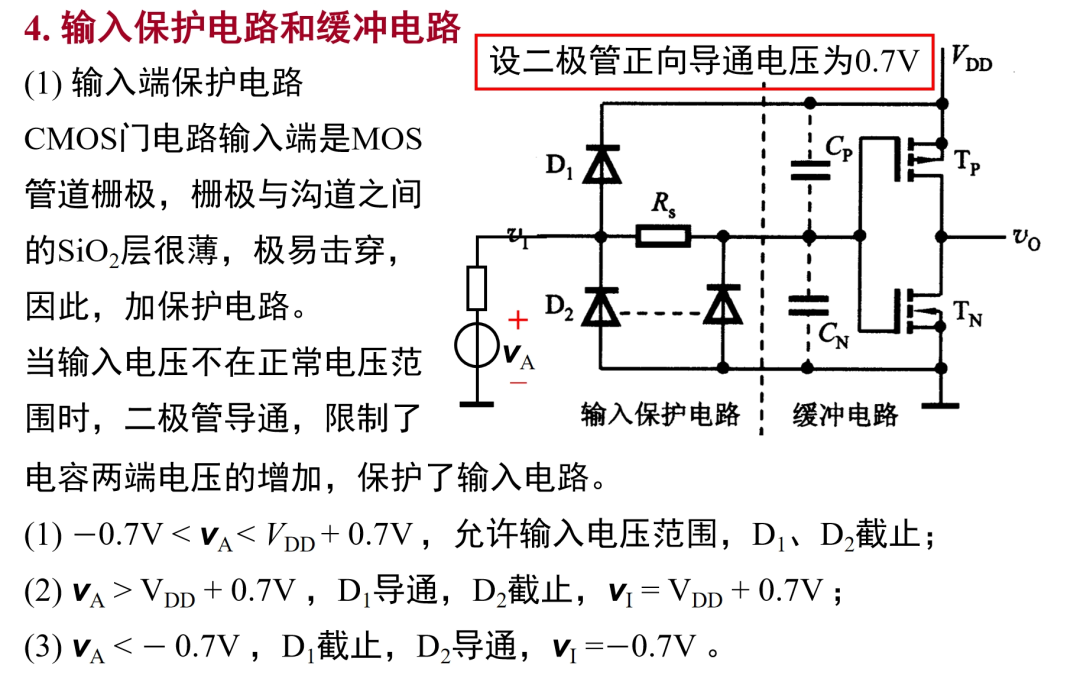

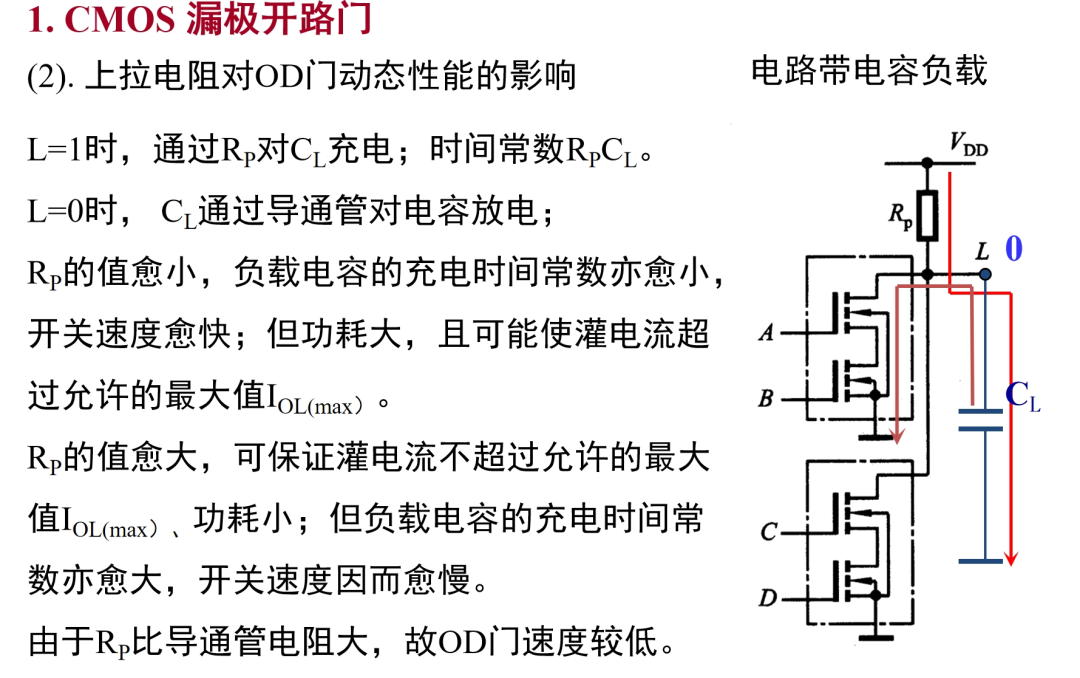

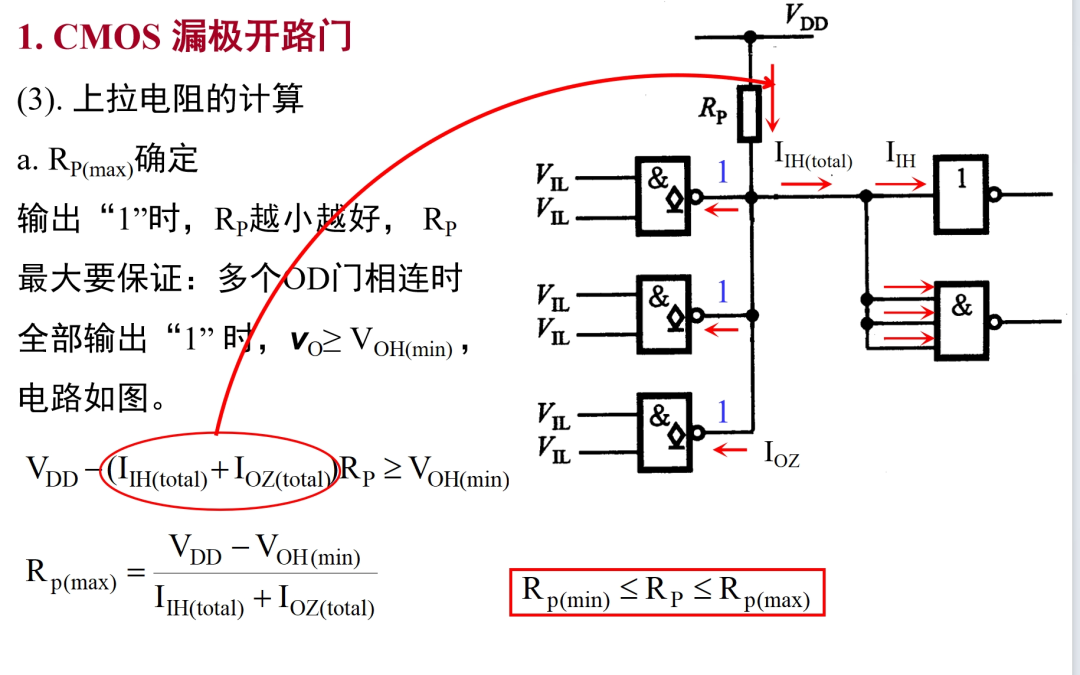

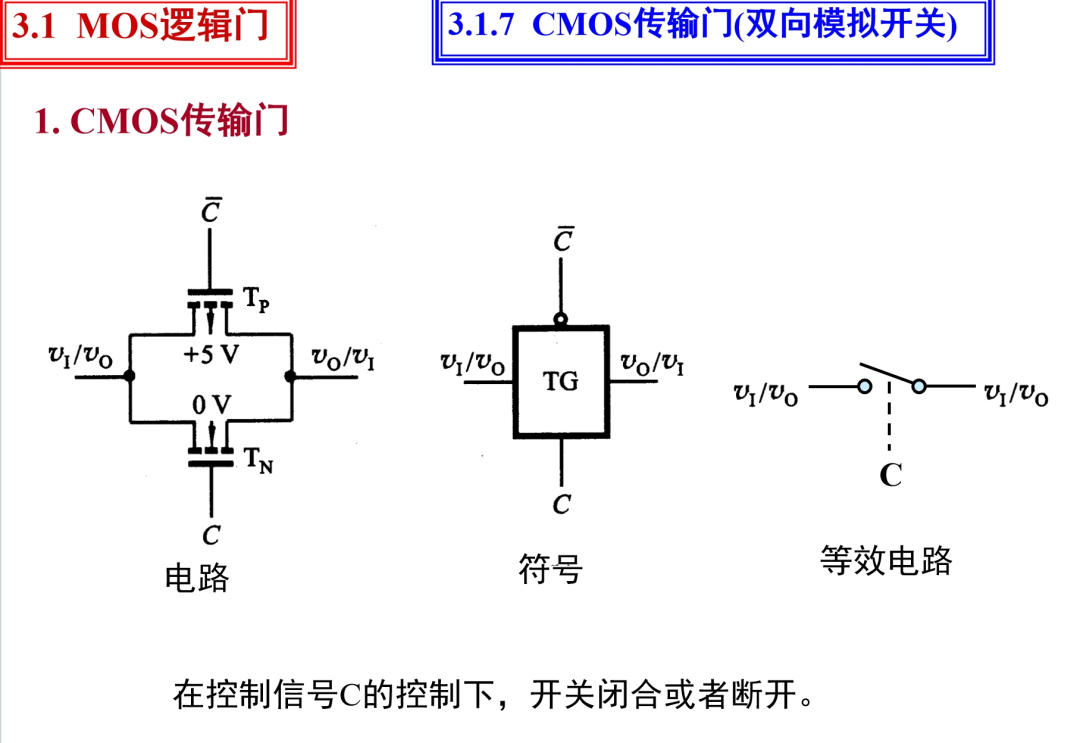

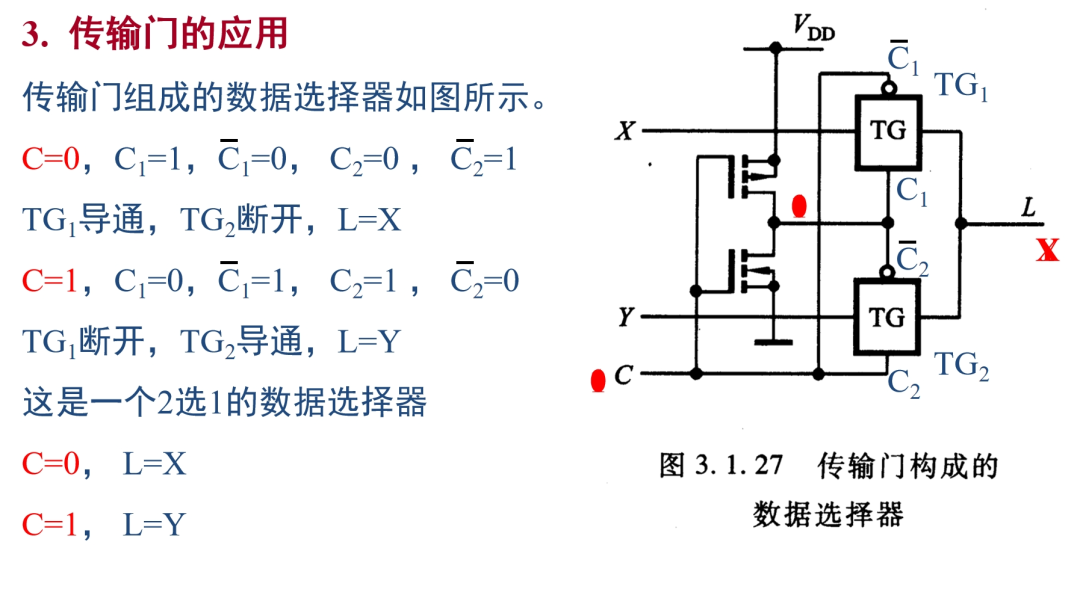

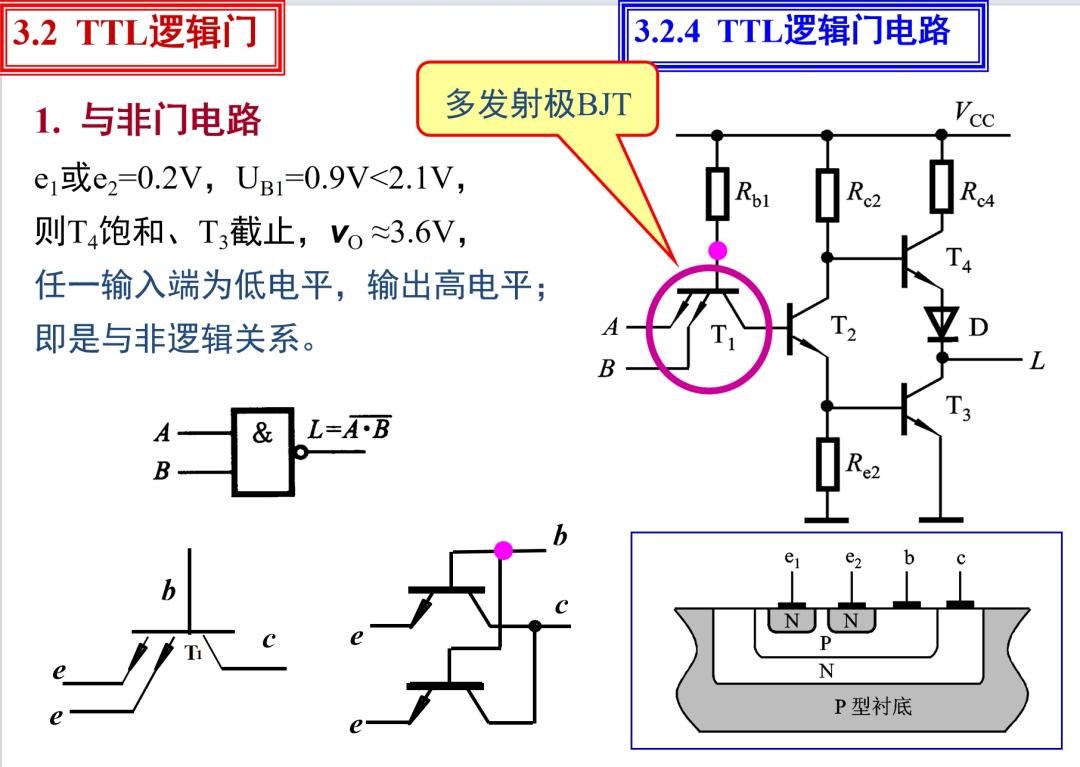

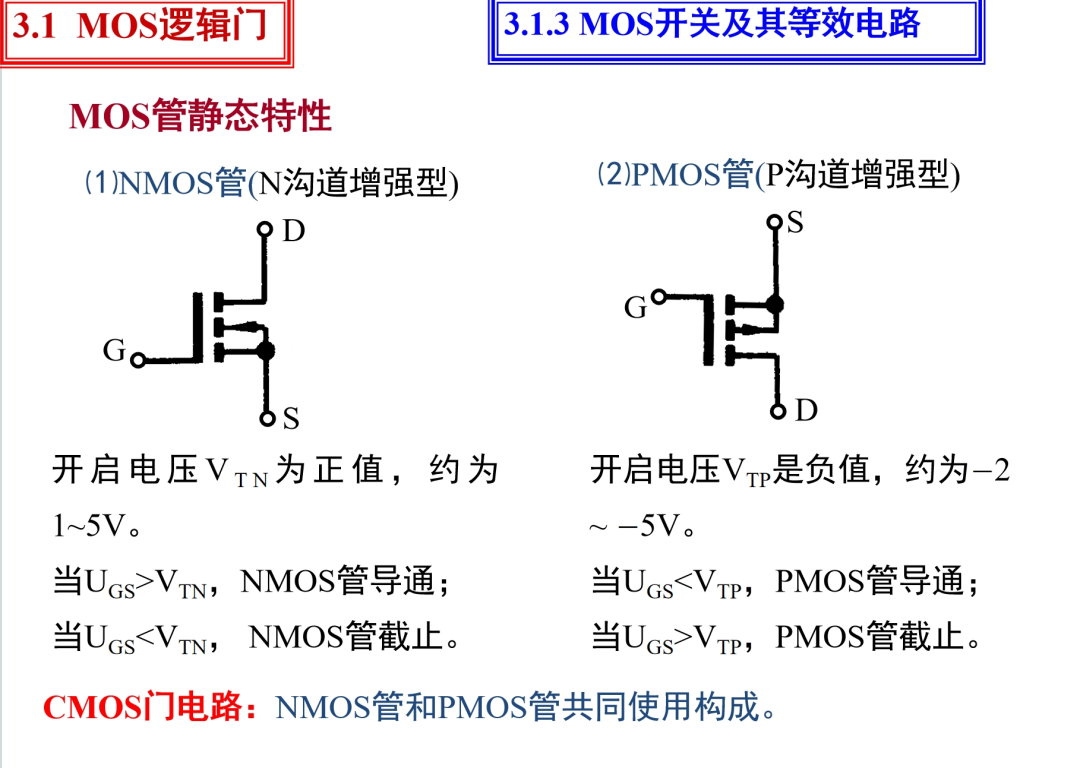

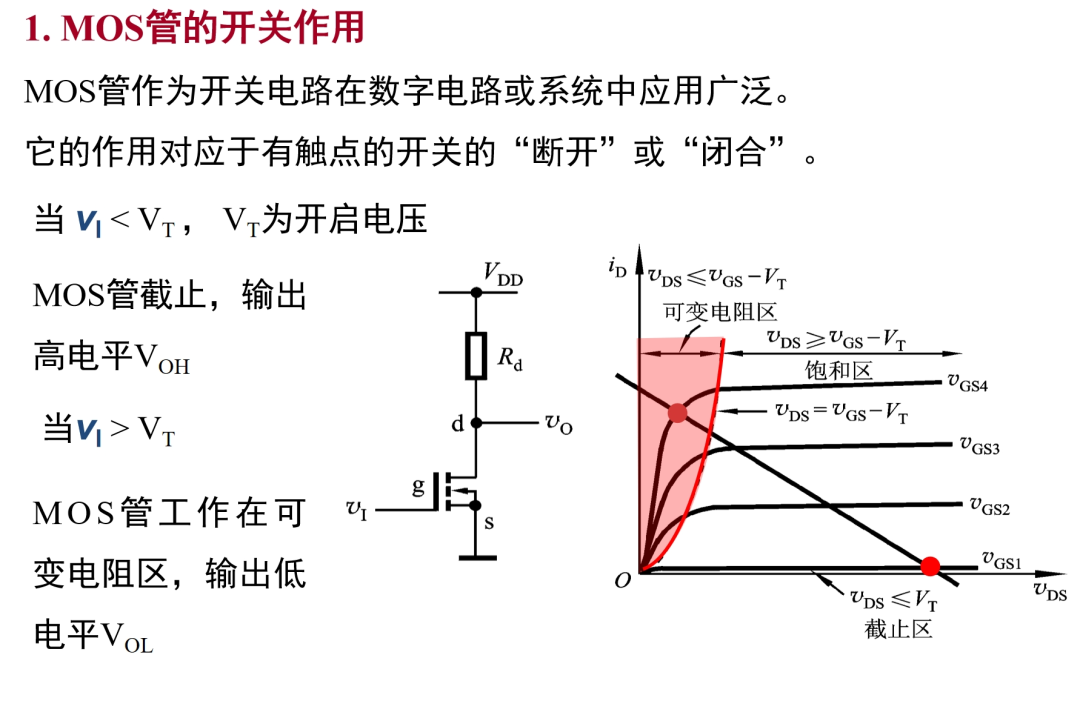

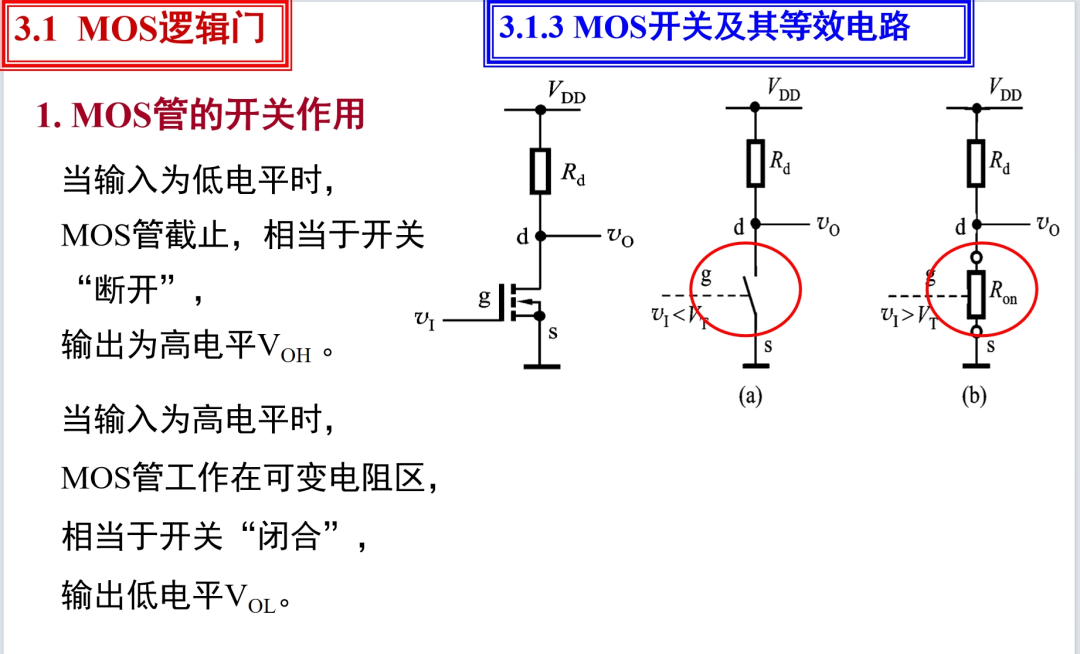

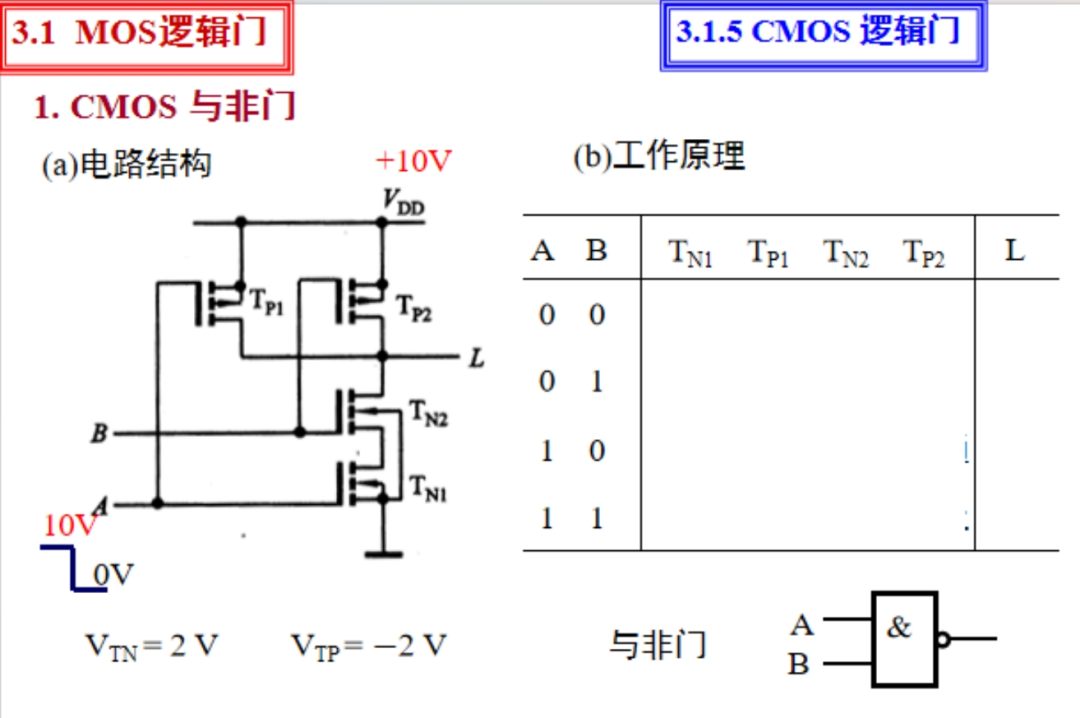

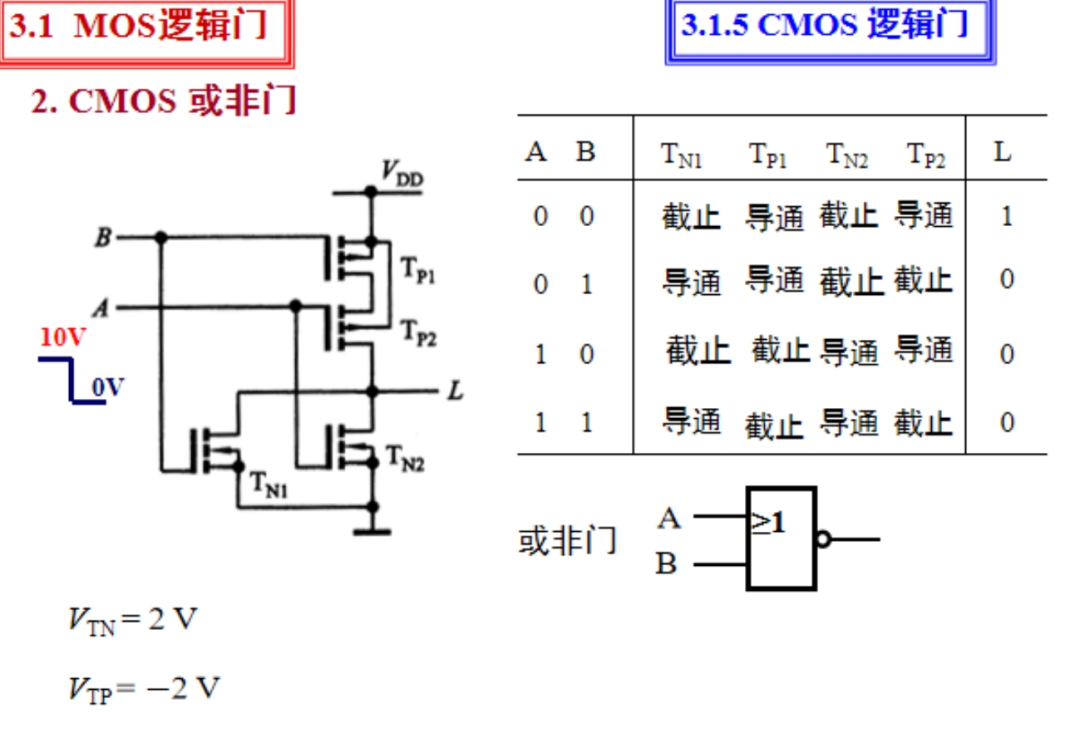

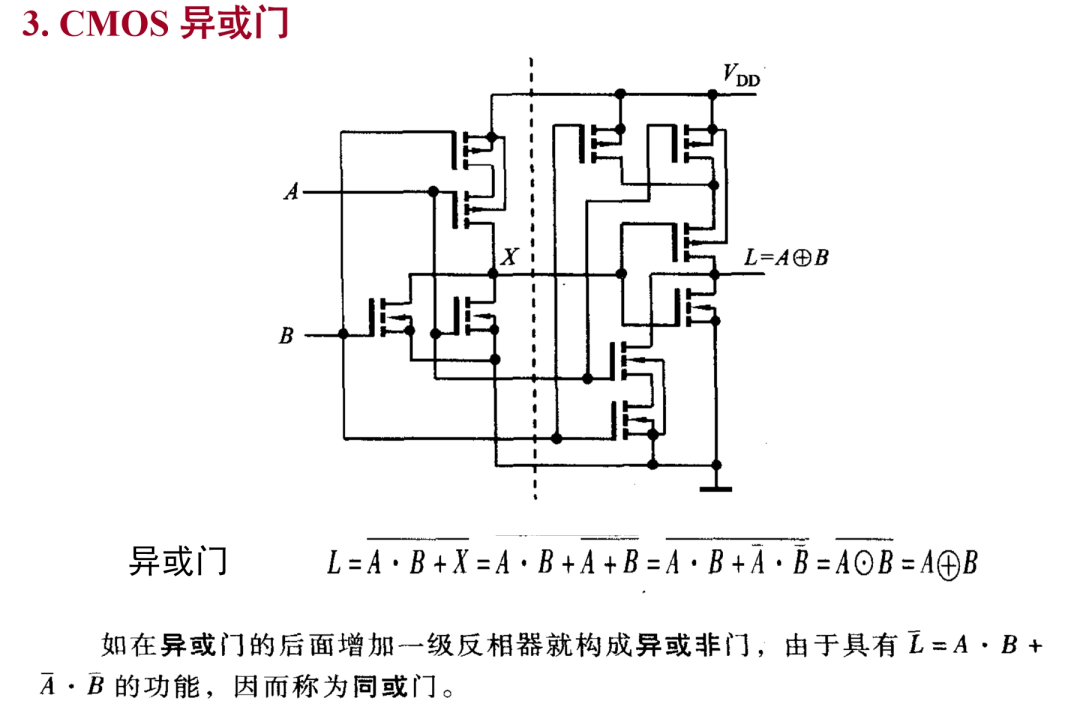

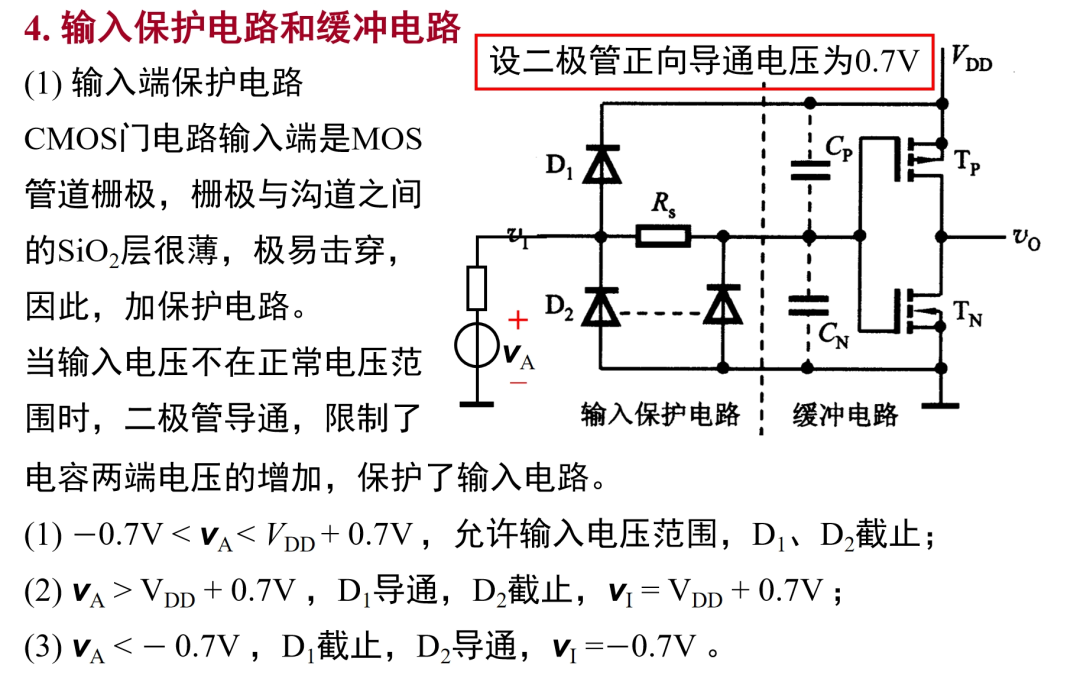

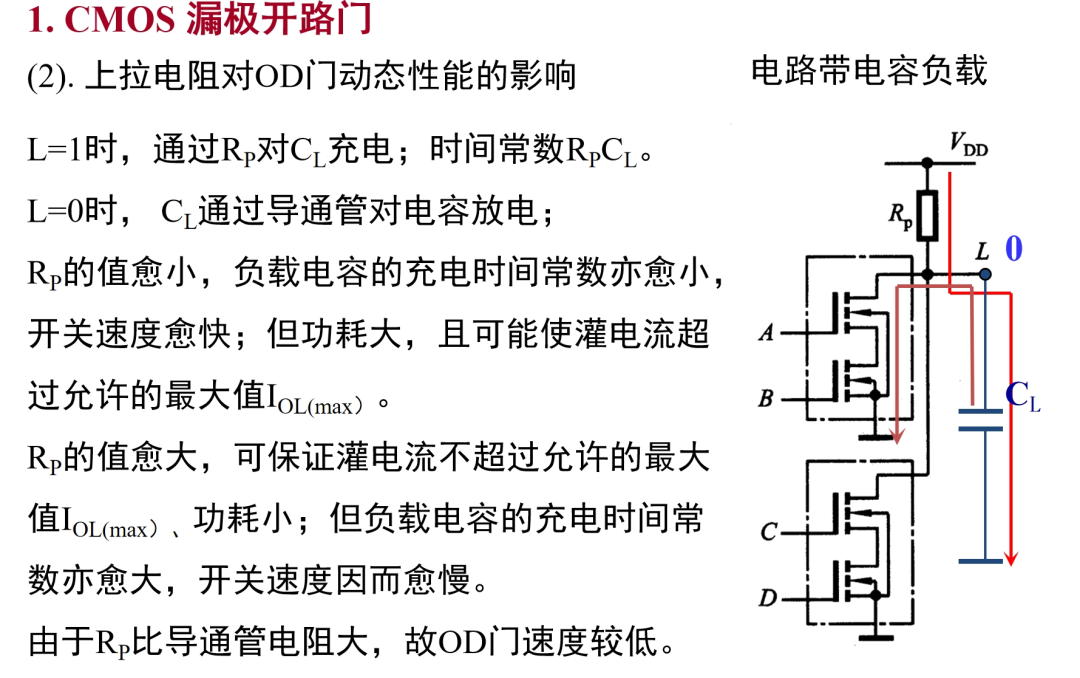

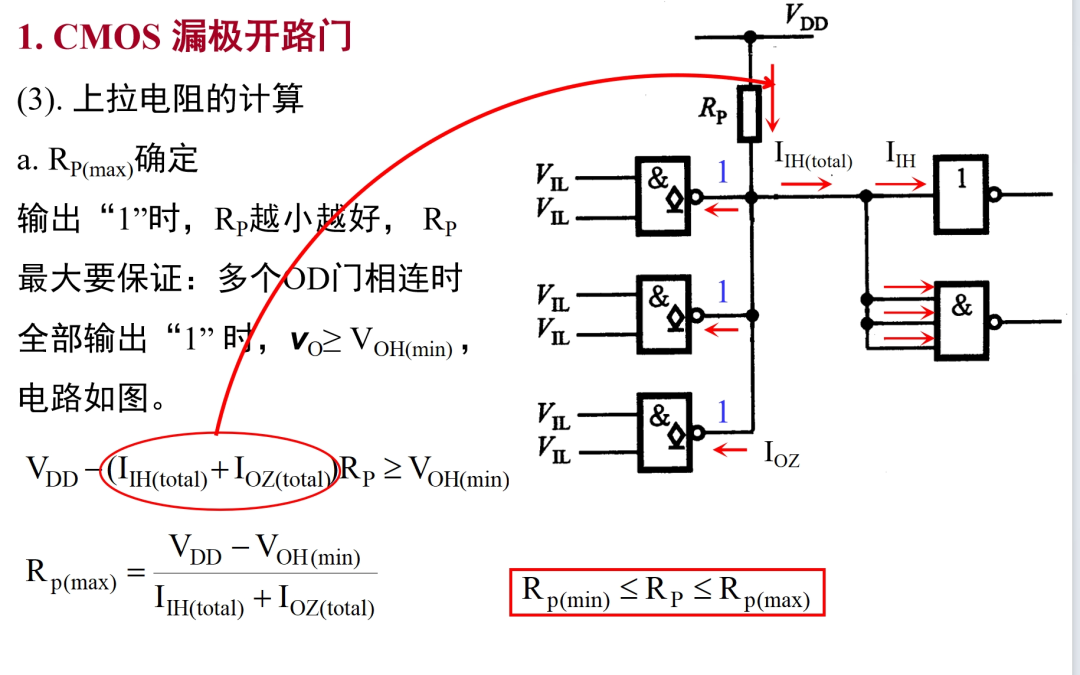

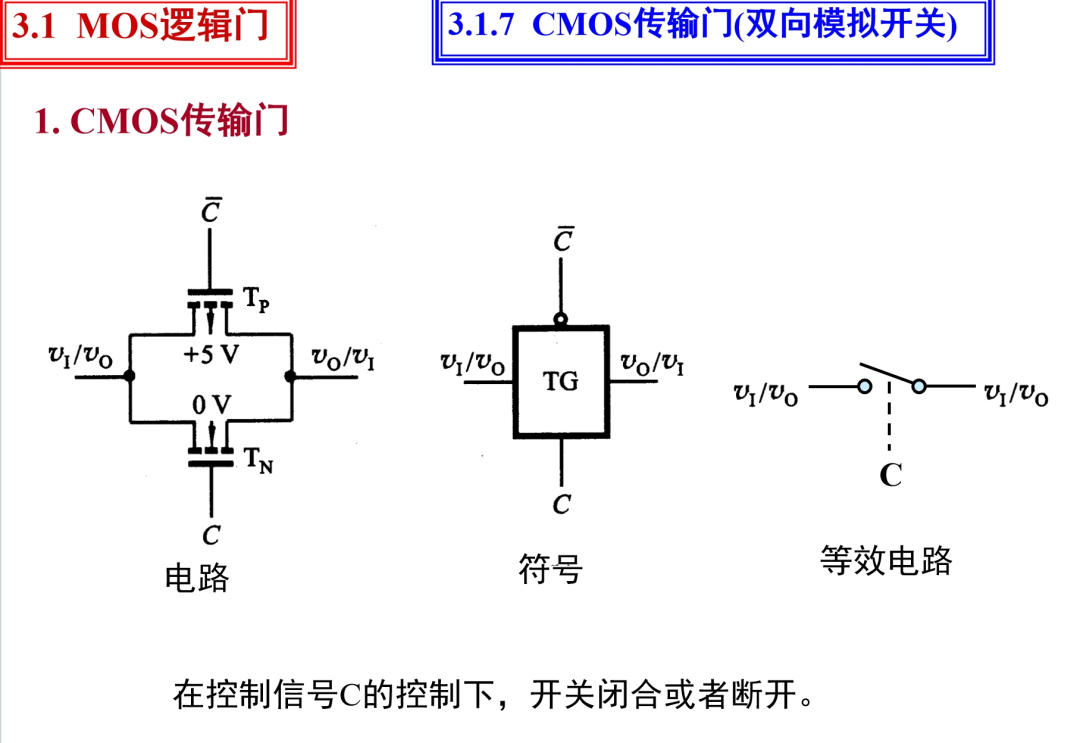

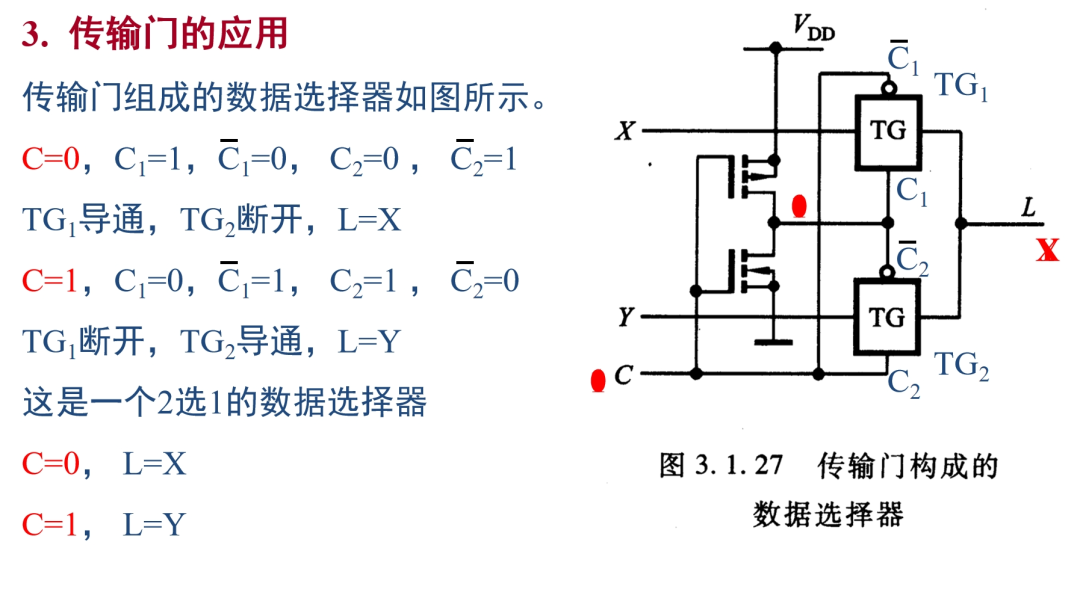

拉电流:驱动门输出高电平时,从驱动门流出的电流,总拉电流和负载门的数量相关。灌电流:驱动门输出低电平时,从驱动门流出的电流,总灌电流和负载门的数量相关。利用场效应管的输出特性,制作出开关电路。下面的知识可以和前两章对应起来学!

输入和输出“反相”,本质是两个场效应管并联!

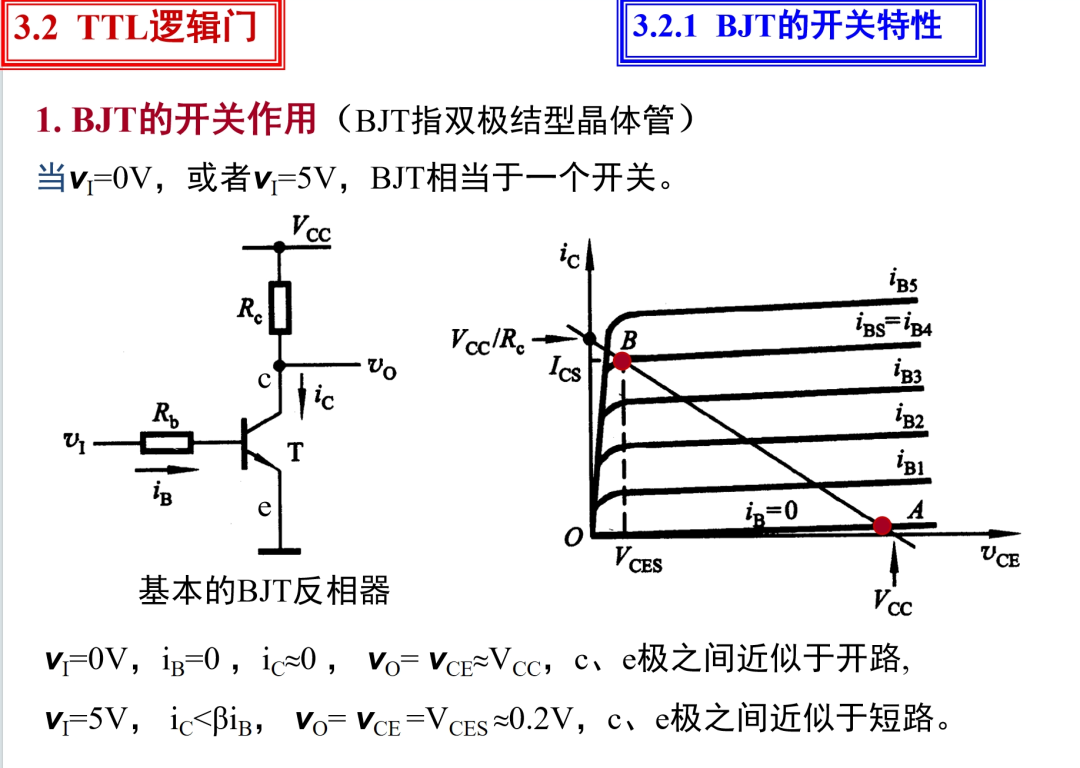

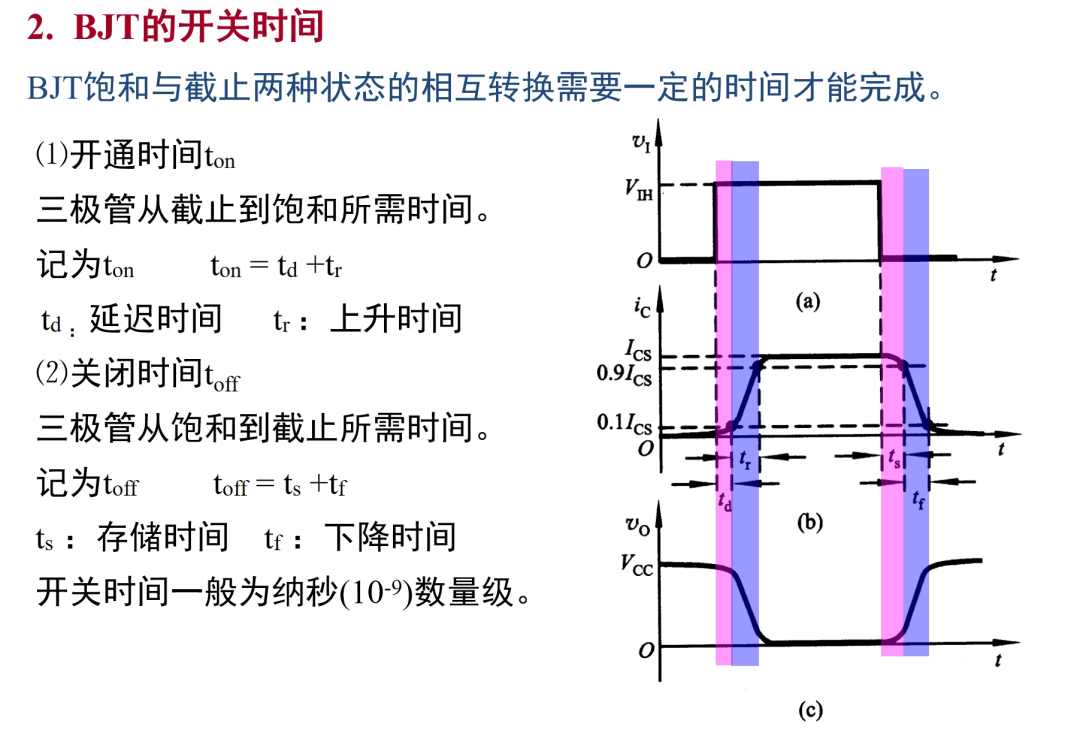

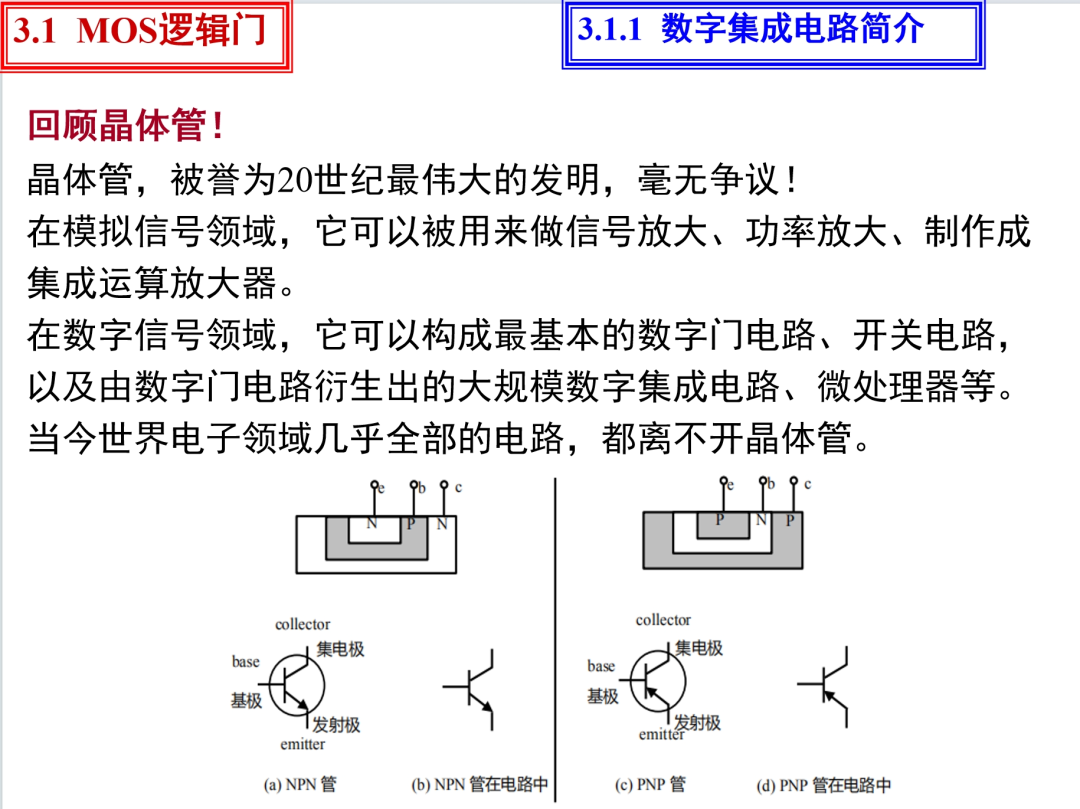

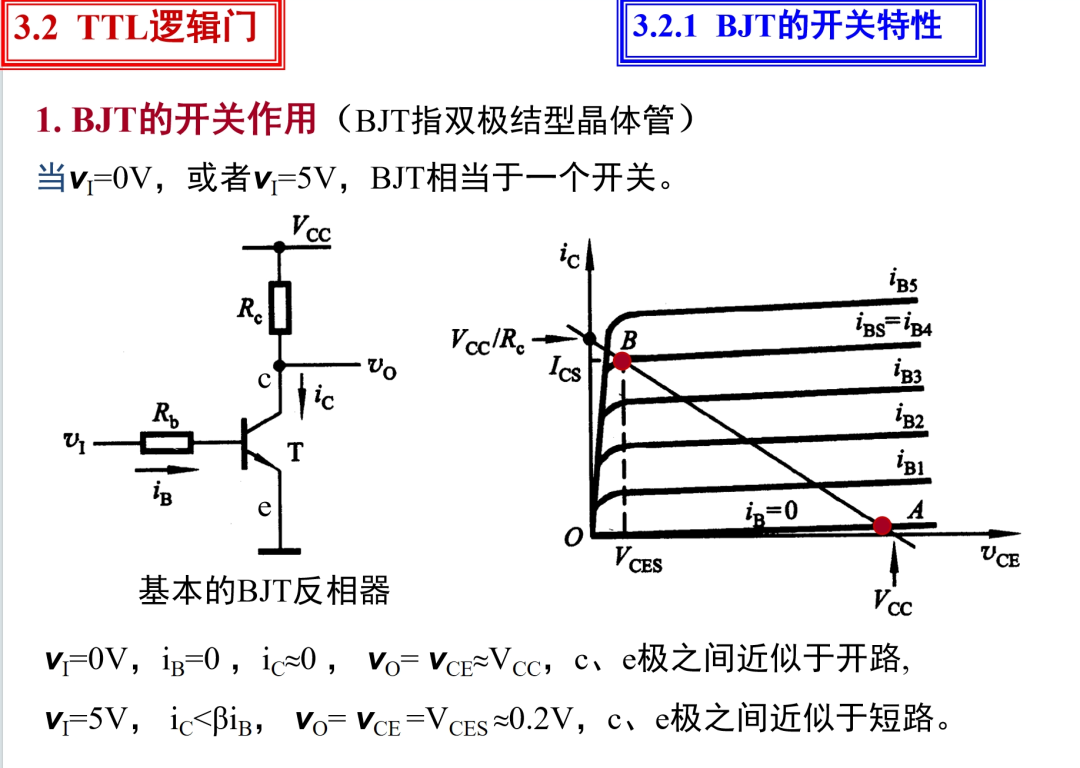

BJT 的全称是双极性结型晶体管(Bipolar Junction Transistor),国内俗称三极管。其实,在英语中,三极管(triode)特指以前的真空电子管形式的三极管,而不是我们现在普遍使用的半导体三极管。而我们现在普遍应用的固态半导体结构的三极管,是1947年发明出来的,标准学名是:双极性结型晶体管(Bipolar Junction Transistor),简称“BJT”。由于最初其功能与管脚跟以前的电子三极管差不多,所以国内业界沿用了“三级管”这个俗称。这个 BJT 比以前电子管结构的三极管,实在优秀太多了:体积小巧、结构简单、不会打碎、无需预加热、功耗损失小、故障率极低、不需要每使用几千个小时就因为灯丝老化而换管子…… 更为逆天的是,后来人们发现,BJT可以做得很微小,然后可以将成百上千的微型BJT组成的电路集成安放在一小块硬币大小的基片上,并将其称为:集成电路(integrated circuit,简称:IC,俗称:芯片)。正是这个BJT的发明,掀开了由电子工业主导的第三次产业革命。

知识点总结!

CMOS和TTL的区别!

1、CMOS是场效应管构成,TTL为双极晶体管构成。

2、COMS的逻辑电平范围比较大,一般在5V~15V,TTL只能在5V下工作。

3、CMOS的高低电平之间相差比较大、抗干扰性强,TTL相差小,抗干扰能力差 。

4、CMOS功耗很小,TTL功耗较大,一般在1~5mA/门。

5、CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当。

6、TTL电路是电流控制器件,而CMOS电路是电压控制器件。

7、TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

3.7 用verilog HDL描述门电路

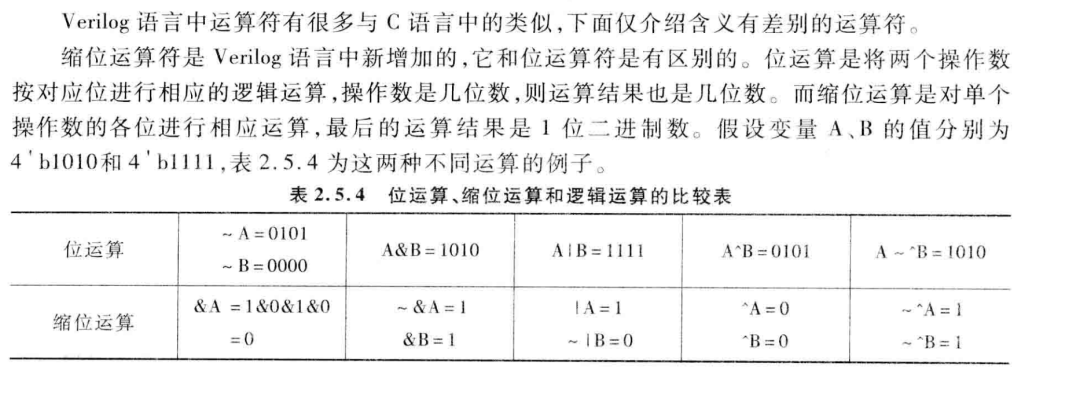

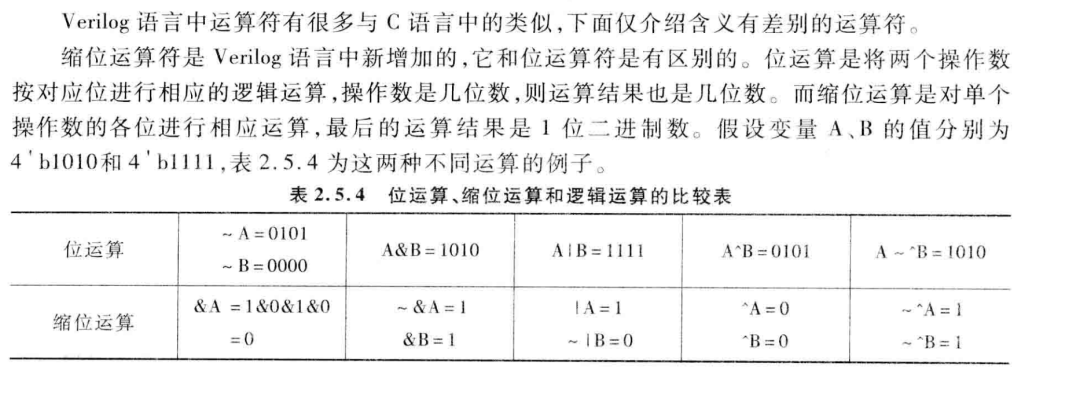

再次来了解基础语法知识!

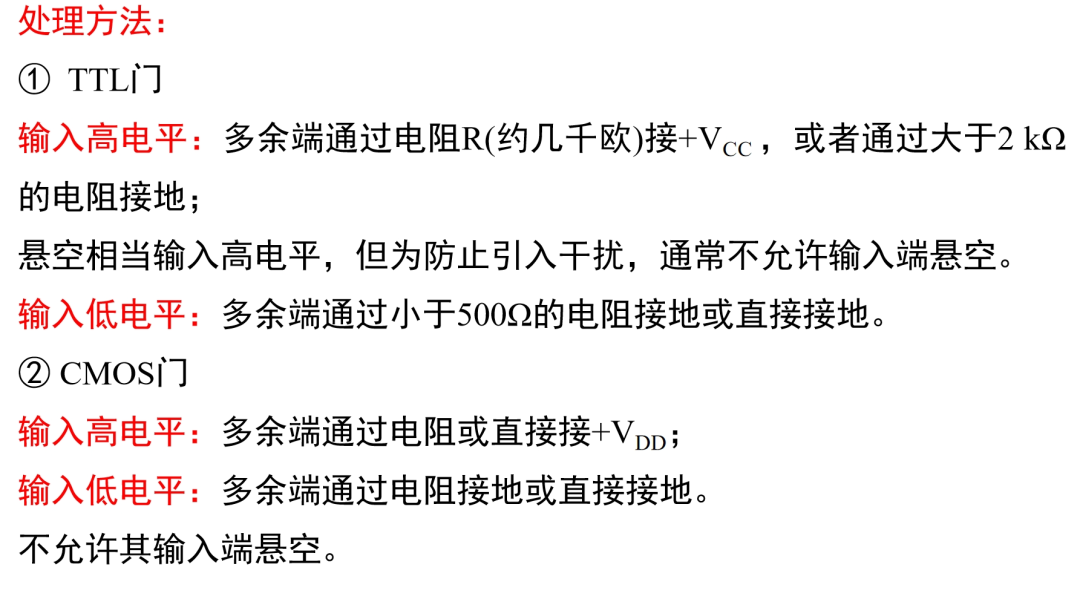

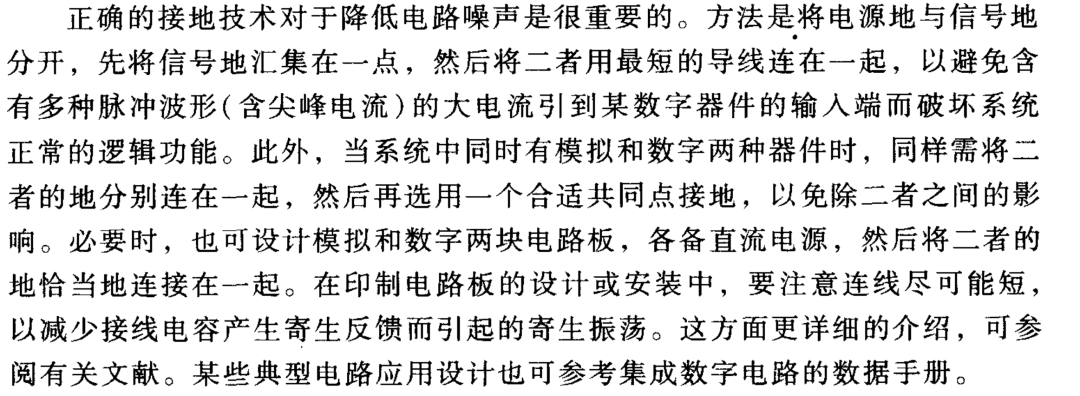

先看教材里面的相关知识!

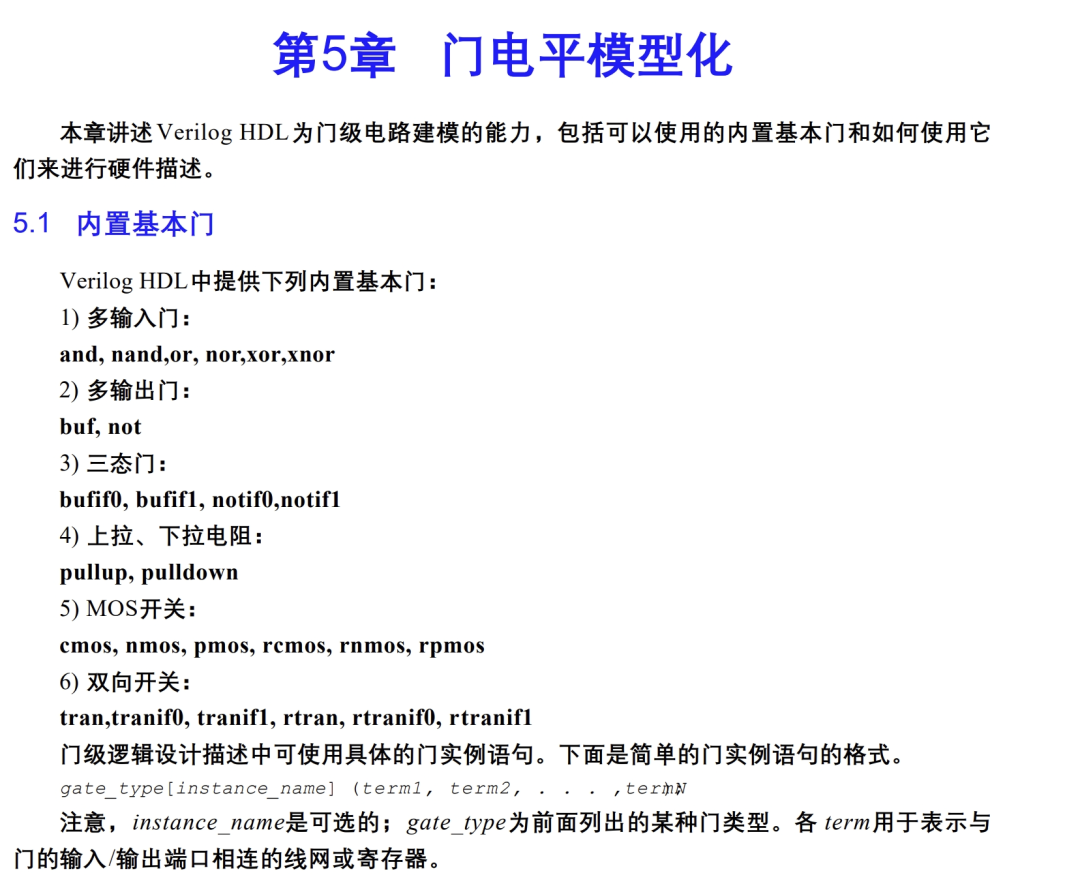

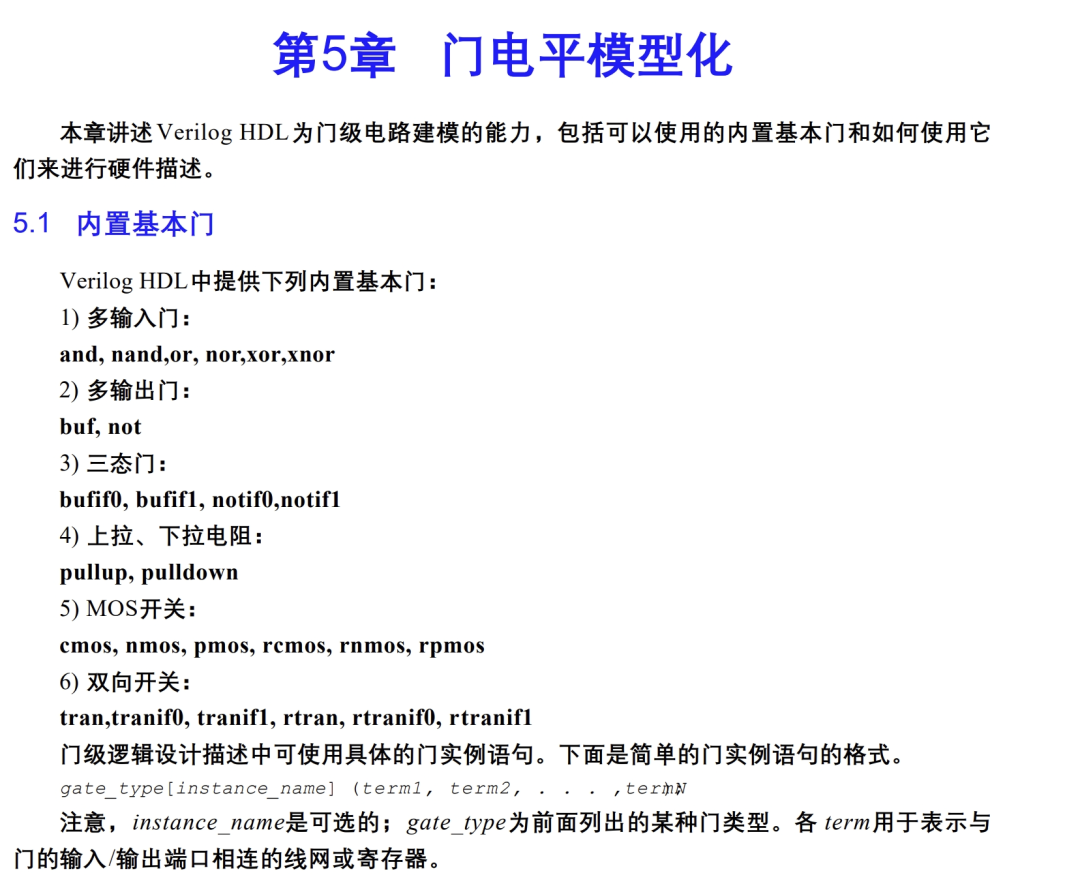

再来看参考资料里面关于门电路的知识!

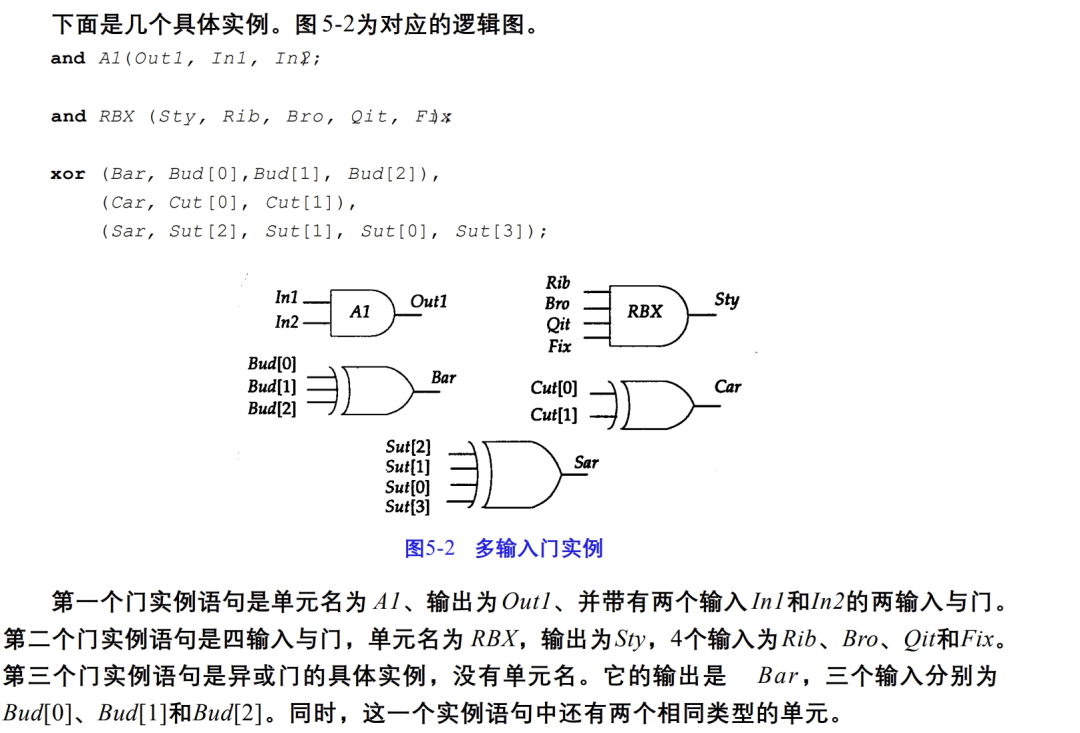

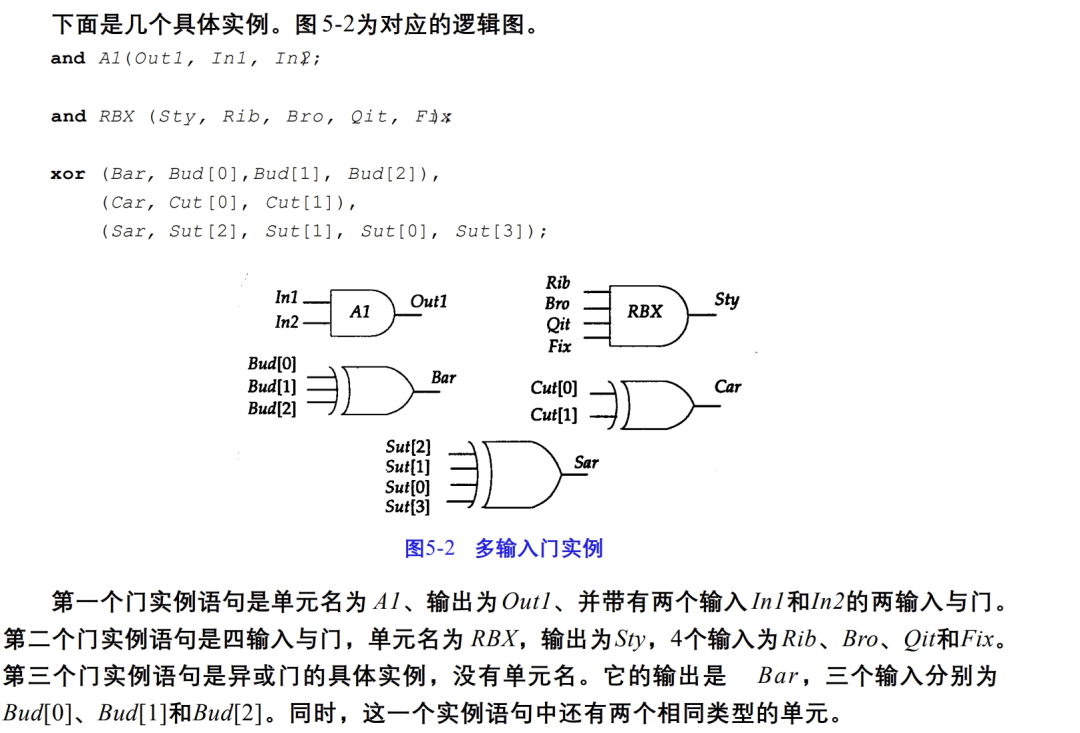

同一门类型的多个实例能够在一个结构形式中定义。

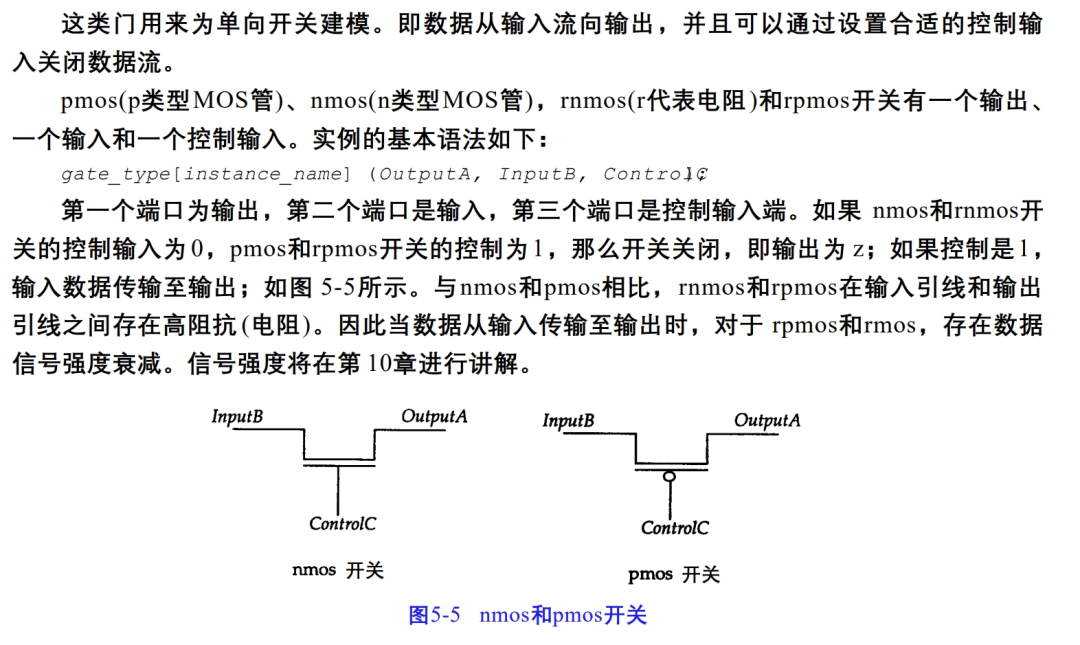

再看教材里面的内容!

试一试,编个程序仿真一下!这些内容对应着资料里面的5.6章节!循序渐进的学!希望同学们能从图书馆借本书进行系统学习!

总结!

.jpg?imageView2/0/w/120/h/120)

.jpg?imageView2/0/w/90/h/90)