Chiplet互连标准—UCIe2.0物理层(RX)

之前介绍了UCIe TX指标,本篇介绍RX指标。

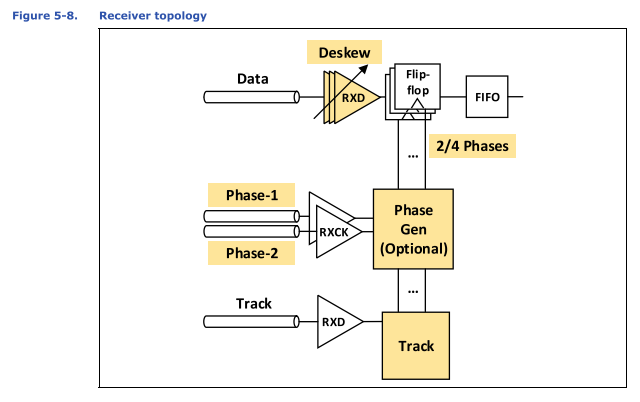

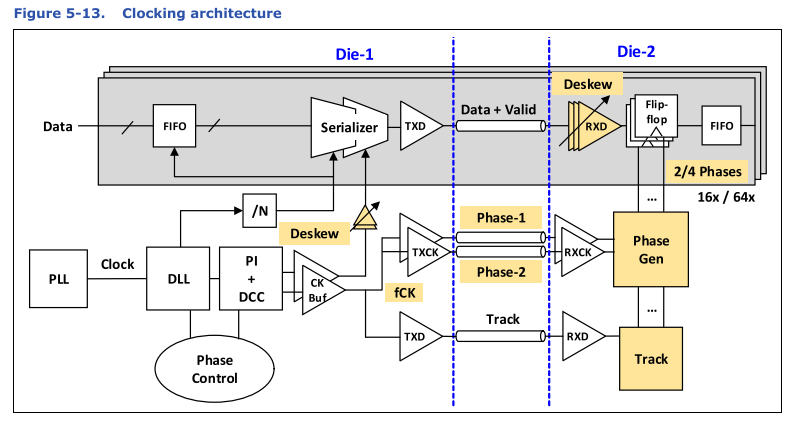

接收器拓扑如图5-8所示,由clocks Receivers, data Receivers, 和 Track Receiver组成。

接收到的时钟用于对输入数据进行采样。接收器必须匹配时钟路径和采样器的数据/有效路径之间的延迟。这是为了最大限度地减少电源噪声引起的抖动的影响。数据接收器可以被实现为2路或4路交错。对于4路交错实现,接收器需要从转发时钟的两个相位内部生成所需的相位。这可能需要接收器上的占空比校正能力。支持的转发时钟频率和相位如第5.5节所述。

在较高的数据速率下,接收机中可能需要deskew能力以实现数据通道之间的匹配要求。接收机deskew(如适用)可在主频带训练期间执行。

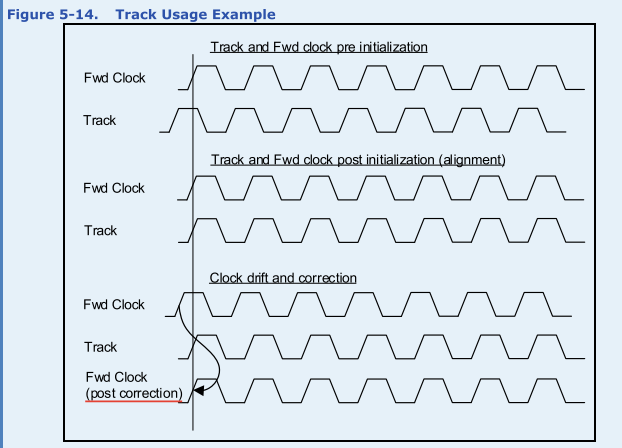

更多详情见第4.5节。在请求跟踪信号时,UCIe模块跟踪发送相位1对准的时钟模式(1010...),并且可以使用跟踪信号来跟踪缓慢变化的电压和温度变化对采样相位的影响(Fig.5-14)。

01

—

RX电气参数

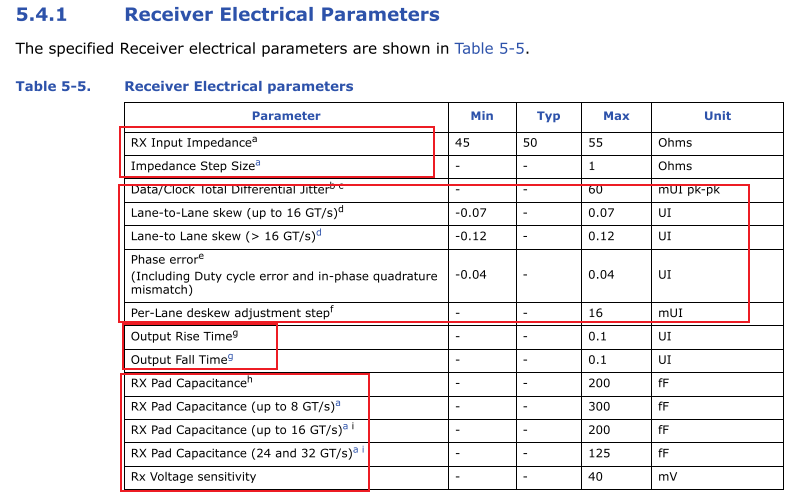

规定的接收电气参数如表5-5所示。

定义了阻抗、抖动、上升下降时间、寄生电容等。

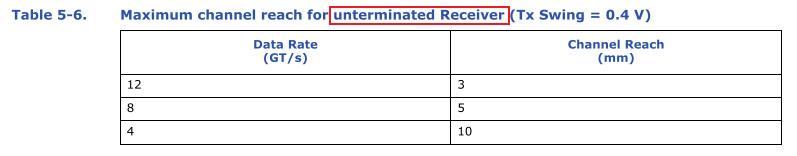

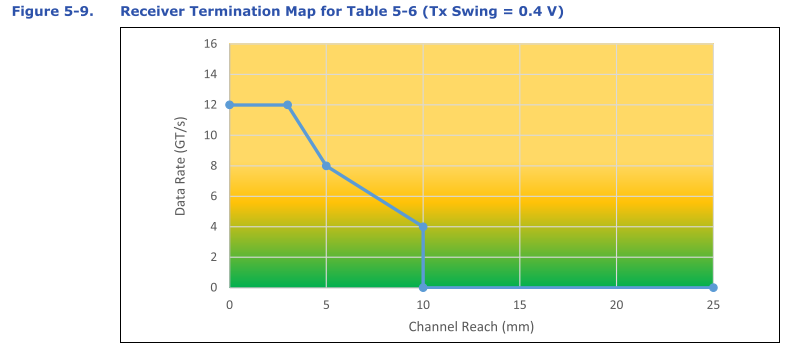

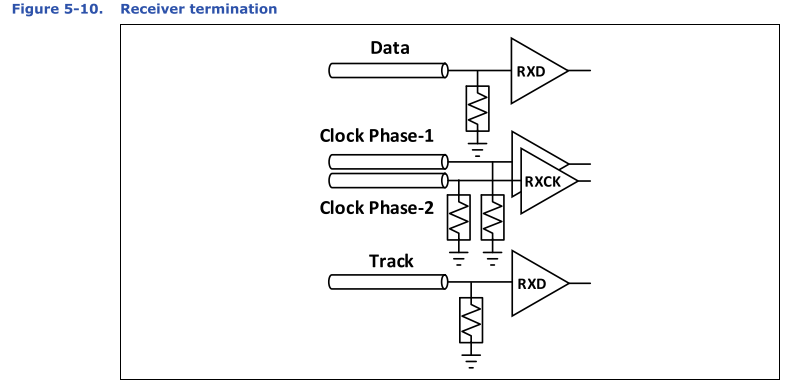

Rx端接仅适用于标准封装模块。先进封装 模块上的所有接收器必须未端接。标准封装上的接收器端接取决于数据速率和通道。表5-6所示为最大数据速率和通道范围组合,建议标准封装模块中的接收器保持未端接状态,以实现最低兼容发射器。图5-9显示了另一种终止要求的表示。图5-9中曲线下方的区域显示了建议标准封装模块中的接收器保持未端接的速度和通道范围组合。所有其他组合均需要端接。如图5-10所示,接收器必须接地。

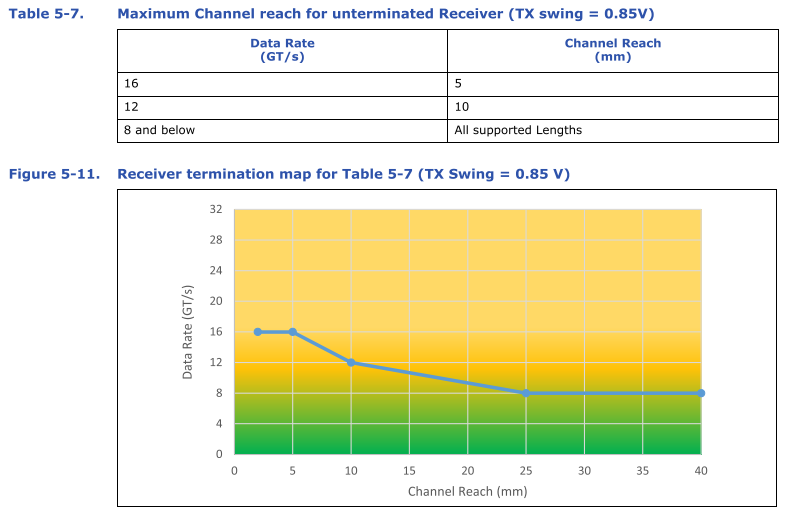

对于更高的发射机摆幅,无端接接收机可以扩展到更长的通道和高数据速率。表5-7显示了发射器摆幅和0.85 V(最大推荐摆幅)的最大数据速率和通道范围组合。图5-11显示了端接要求的另一种表示。图5-11中曲线下方的区域显示了速度和航道延伸范围建议标准封装模块中的接收器保持未端接的组合。

02

—

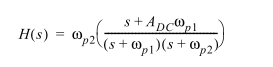

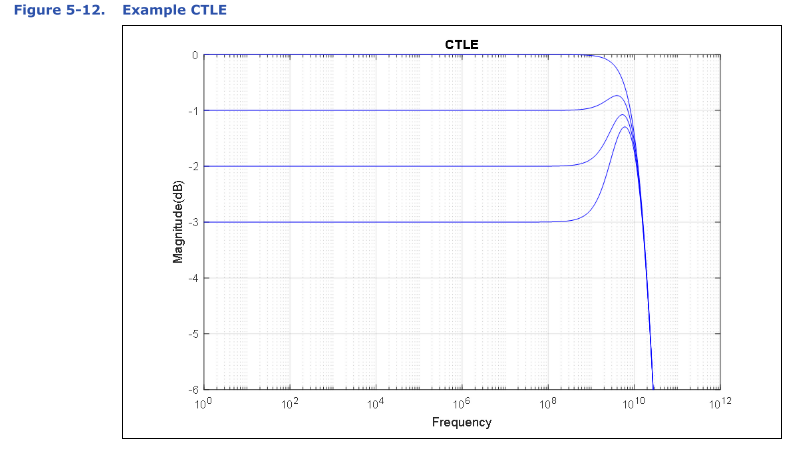

24和32 GT/s接收均衡

接收均衡可以以24 GT/s和32 GT/s的数据速率实现。这使得即使在TX均衡不可用时也能够进行链路操作。实现方式可以是CTLE、电感峰化、1抽头DFE或其他。预期的RX均衡能力相当于一阶CTLE。一阶CTLE的示例传递函数曲线如图5-12所示,相应的方程如下所示:

03

—

时钟

图5-13显示了前向时钟架构。每个模块都支持两相前向时钟。保持模块内所有数据通道和有效信号之间的匹配至关重要。接收器必须在接收器时钟分配和数据/有效接收器路径之间提供匹配的延迟。这是为了最大限度地减少电源噪声引起的抖动对链路性能的影响。在发射机上进行相位调整,如图5-13所示。需要链路训练来设置相位调整的位置,以最大化链路裕度。

在更高的数据速率下,接收器眼容限可能很小,并且数据通道(包括有效通道)之间的任何skew都可能进一步降低链路性能。在高数据速率下,发射机必须支持逐通道deskew。

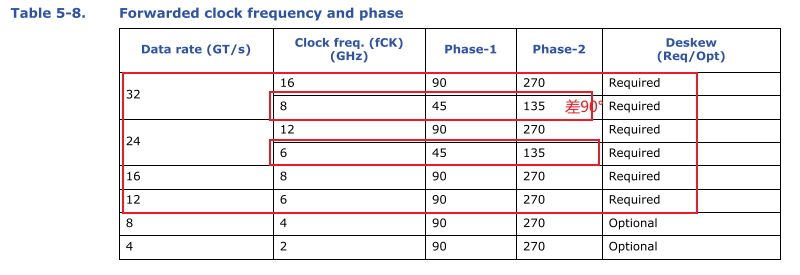

该规格支持数据速率(24 GT/s和32 GT/s)下的四分之一速率时钟频率。转发时钟发射机必须支持正交相位,以及这些数据速率下的差分时钟(以实现四分之一速率或半速率接收机实现)。表5-8显示了不同数据速率下必须支持的时钟频率和相位。转发时钟相位在链路调试和训练期间协商(参见第4.5.3.3.1节)。

接收器可选择支持差分时钟或正交时钟。能力寄存器在表9-47中定义,并在链路协商开始时通告。请注意,为了实现与最大数据速率较低的设计的互操作性,差分时钟必须始终在16 GT/ s及以下使用,与24 GT/s和32 GT/s的选择无关。

Track信号:

跟踪信号可用于执行重新校准,以调整接收器时钟路径,以适应缓慢变化的电压,温度和晶体管老化条件。

如图5-13所示,当UCIe模块请求时,UCIe模块伙伴发送一个时钟模式(1010...),该时钟模式与其轨道发射机上转发时钟的相位1对齐。

下面提供了一个使用跟踪信号校准接收器上数据和时钟之间缓慢变化的温度和电压相关延迟漂移的示例。

跟踪使用与数据相同类型的Tx驱动器和Rx接收器(参见图5-13)

。与转发时钟的相位1对齐的时钟模式从轨道发送器发送并在轨道接收器上接收。在接收器侧的初始化和训练(MBTRAIN.RXCLKCAL)期间,可以校准任何初始偏斜。

在运行时,可以检测数据和转发时钟之间的任何漂移。检测漂移的一种方法是用转发的时钟对Track进行采样。可以收集特定于实施方式的样本数量,如果需要,可以对其进行平均,并将其用于漂移检测。然后可以在转发的时钟上校正该漂移(如果需要)。

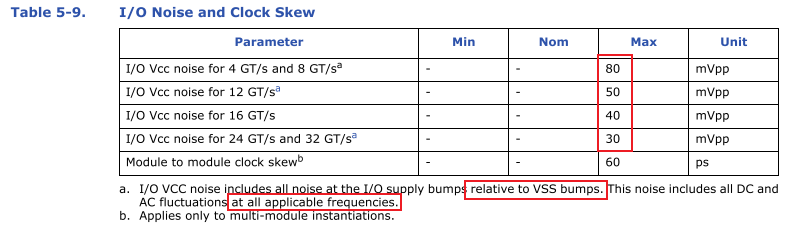

5.6电源噪声和clock skew

I/O噪声和数据模块之间的时钟偏差应在表5-9规定的范围内。

速率越高,纹波要求也越高。

由于不同的微凸块最大电流容量和功率输送要求,先进封装中的PHY可以TX向RX电路提供I/O电源。由于低电流消耗,强烈建议边带电源电压位于始终导通的电源域。

后续分享互连指标。

参考文献:

[1]:UCIe2.0 SPEC

end