EDI14.20 New Feature Introduction-iCTS在深纳米工艺下的先进性

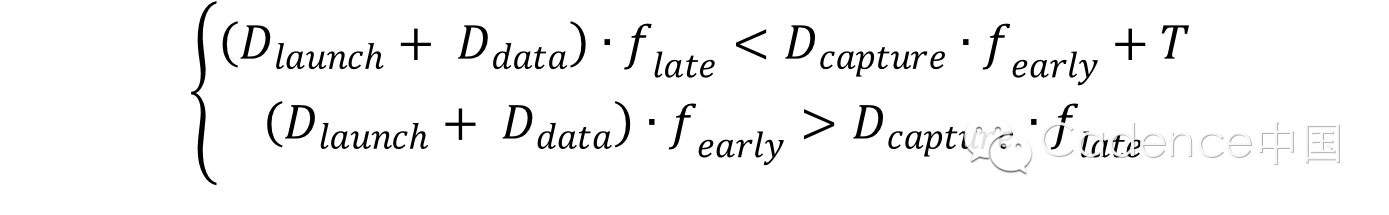

随着半导体制造工艺地不断演进,更多的功能模块被引入SoC中,系统设计复杂度不断地提高。而在多模式多端角(MMMC)下,OCV的影响逐渐成为时钟树设计的难题。以一条简单的时序路径为例,我们可以迅速写出一组简单的方程组来展示建立时间与保持时间的关系,如下所示.

将上述方程组联立与整理之后,可以得到下式:

其中,时钟周期T与OCV的因子(fearly和flate)在一般设计流程中是固定的,同时在CTS阶段,数据路径的延迟Ddata也是不变的。因此,为了能够维持更高更快的时钟工作频率,并且满足各种时序约束的基础之上,我们只能够通过最小化时钟网络延迟,即Dlaunch和Dcapture,来得到高性能的时钟树结构。

其中,时钟周期T与OCV的因子(fearly和flate)在一般设计流程中是固定的,同时在CTS阶段,数据路径的延迟Ddata也是不变的。因此,为了能够维持更高更快的时钟工作频率,并且满足各种时序约束的基础之上,我们只能够通过最小化时钟网络延迟,即Dlaunch和Dcapture,来得到高性能的时钟树结构。

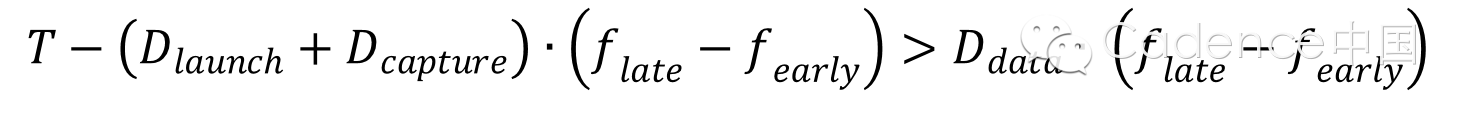

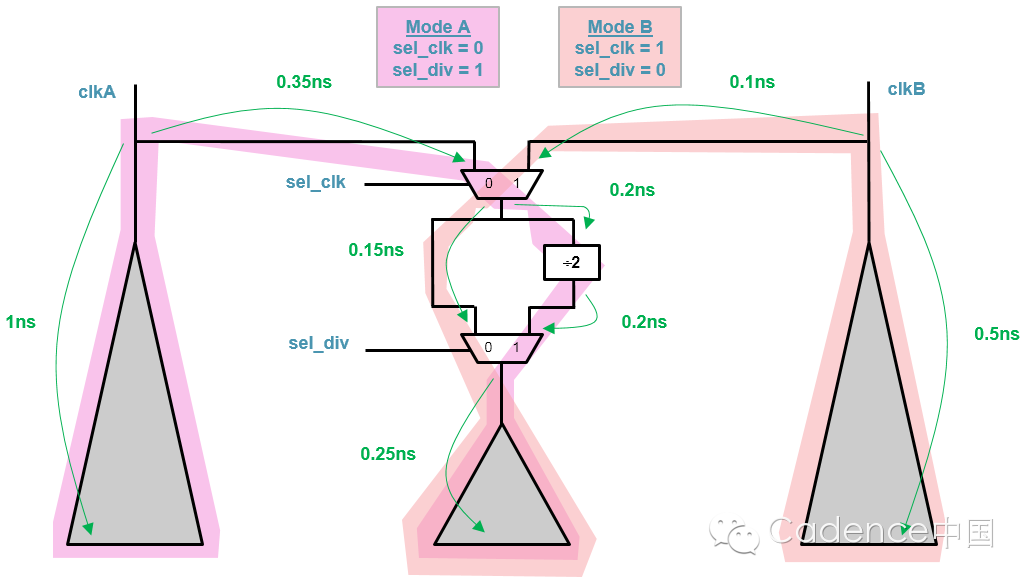

传统的CTS工具是基于树形结构的综合策略,我们通常称之为“Tree-based CTS”。这种策略在面对较复杂的时钟树结构时,很难做到最优的时钟网络延迟。如图-1所示,当两个时钟路径存在共同的叶节点,且在共同路径中存在重汇聚点时,传统CTS策略很有可能在重汇聚(re-convergence)的路径上进行过度优化,从而导致CTS插入了多余的缓冲单元来平衡时钟skew。

当遇到此类情况时,我们不得不手动干预传统的CTS策略。通常来说,我们会采用多通道“multi-pass”的方法将时钟逻辑单元打断,然后分别采用不同的通道进行CTS来尽可能平衡时钟树在各个模式下的延迟。那么,问题来了。当面对深纳米工艺和高性能挑战的时候,我们不得不借助有用偏差技术——Useful Skew,来尽可能提高芯片稳定工作的性能,那么在CTS阶段牺牲时钟延迟与功耗来最小化skew并不是明智之举。因此,我们需要在时钟延迟、时钟功耗和时钟skew之间得到更加有效而合理的组合。

区别于传统CTS工具,Cadence EDI 14.20 (Oct. 2014)采用全新的CTS引擎——iCTS。iCTS是一种基于图表结构的CTS策略,又称“Graph-basedCTS”。这种CTS策略可以让基于MMMC下的SDC得到精确理解。每一种SDC模式的时钟树都被转化为一个新的“skew group”,而这个skewgroup将包含此模式下的所有时钟叶节点。当时钟树结构存在上述重汇聚和堆叠的情况时,同一个时钟树将在不同的模式下追溯得到不同的时钟节点,从而产生不同的skew group定义。

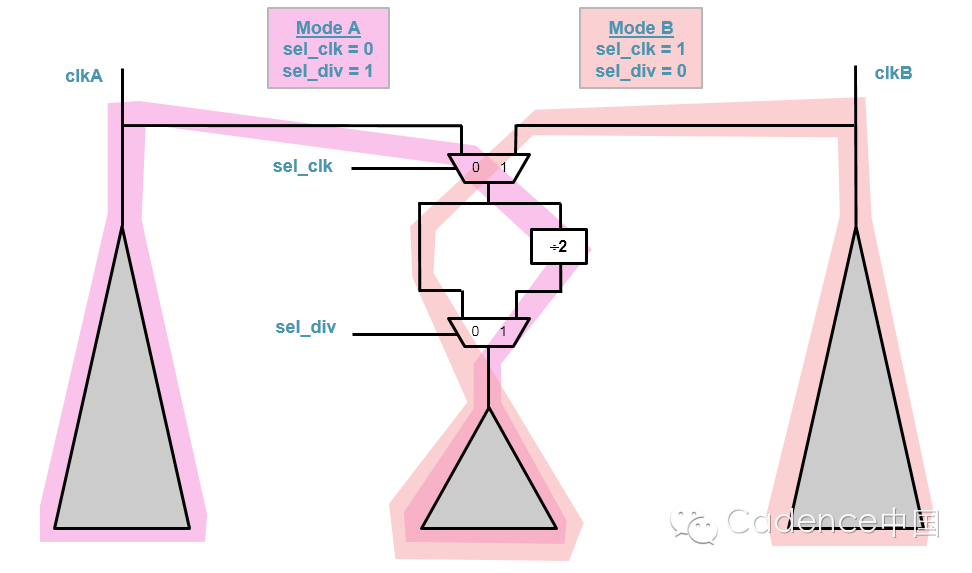

为了实现上述功能与特性,iCTS将通过4个步骤进行CTS。首先,iCTS需要从多模式的SDC中抽取时钟树信息,建立skew group组。然后,建立最小时钟延迟的全局时钟树结构,此时不考虑时钟偏差,见下图。 接着,iCTS将来自不同MMMC下时钟约束映射到每一组skew group上,并且通过iCTS独有的全局解析算法逐步解析时钟延迟、时钟功耗和时钟skew之间的关系,最终得到一组最优解,如下图所示例。

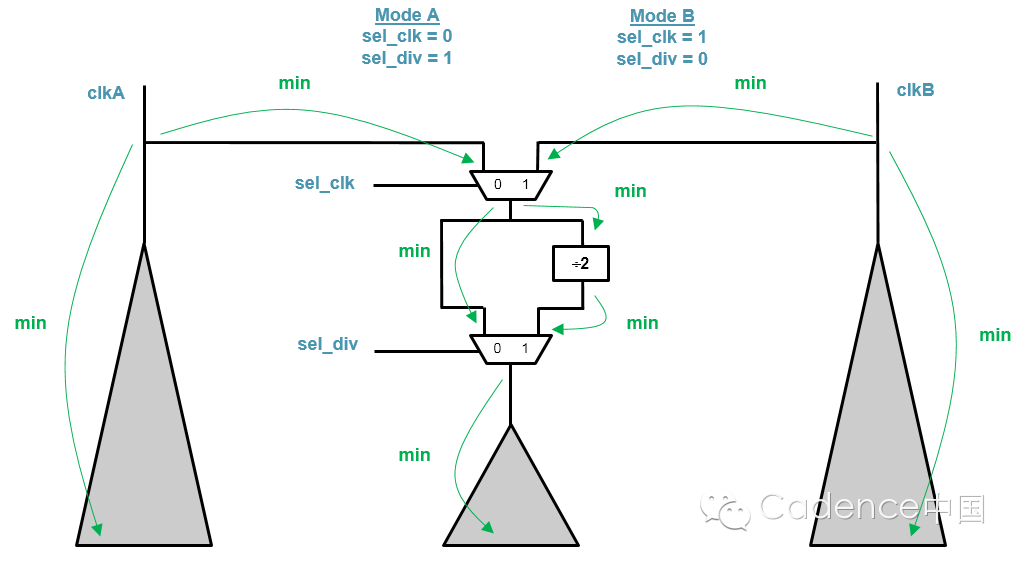

接着,iCTS将来自不同MMMC下时钟约束映射到每一组skew group上,并且通过iCTS独有的全局解析算法逐步解析时钟延迟、时钟功耗和时钟skew之间的关系,最终得到一组最优解,如下图所示例。 相比传统的CTS工具,用户不仅仅可以指定时钟树的最大延迟、最大skew等约束,还可以针对不同skewgroup定义不同的时钟约束,从而扩大了用户的控制范围。那么,采用Graph-based iCTS的优势就得到了展现:

相比传统的CTS工具,用户不仅仅可以指定时钟树的最大延迟、最大skew等约束,还可以针对不同skewgroup定义不同的时钟约束,从而扩大了用户的控制范围。那么,采用Graph-based iCTS的优势就得到了展现:

1. 不同skew group的叶节点允许存在交集;

2. 一个skew group的时钟信号可以来自多个时钟源;

3. 不同的skew group可以包含多个重汇聚点;

4. 不同的skew group还可以人为地进行优先级排序;

5. 可以对每个skew group定义不同的ignore叶节点;

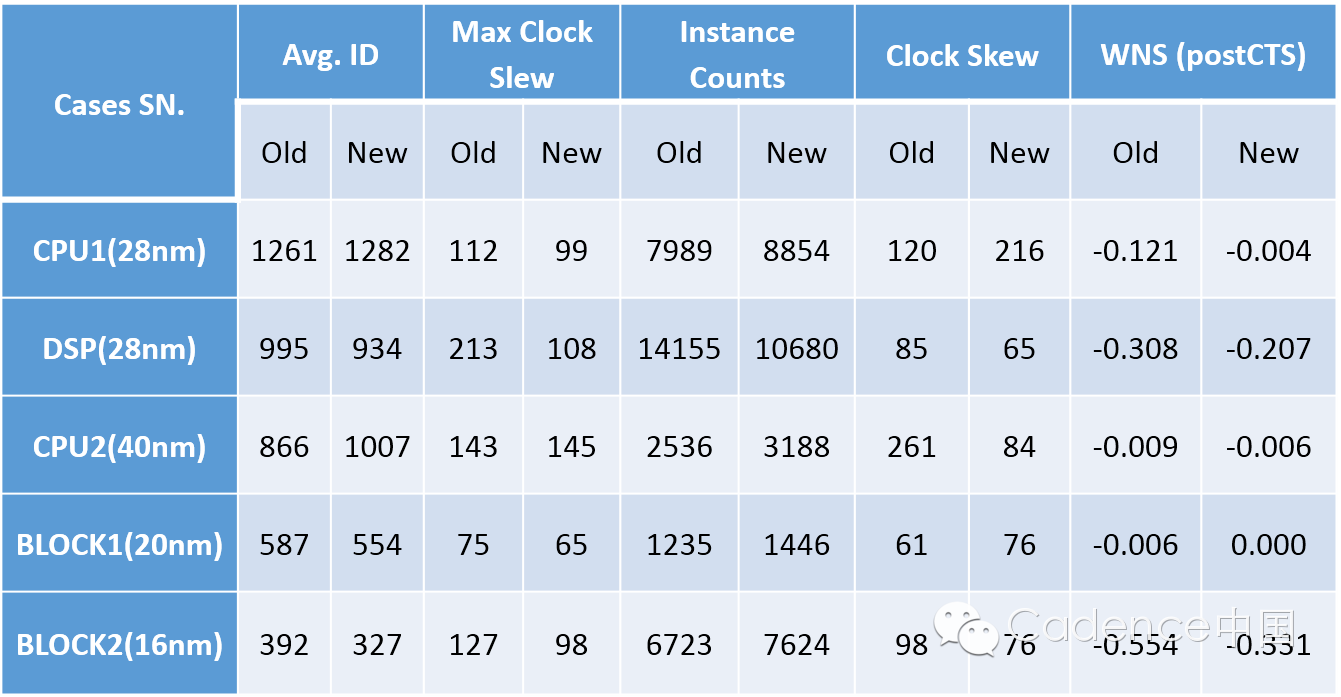

基于上述描述,通过iCTS可以获得更加适用于深纳米工艺和高性能要求的时钟树结构。我们在几个关键的设计中,对两种CTS工具进行了对比,如下表所示。

在EDI14.20中,iCTS将作为默认的CTS工具来取代原有的CTS工具。通常情况下,用户不需要进行流程脚本的修改就可以无声无息地得到iCTS生成的时钟树结构,从而无缝连接到流程的下一步骤。作为EDI 14.20最重要的革新部分,iCTS将在更多、更先进的设计中大展身手,并给用户提供更加优质的体验。

在EDI14.20中,iCTS将作为默认的CTS工具来取代原有的CTS工具。通常情况下,用户不需要进行流程脚本的修改就可以无声无息地得到iCTS生成的时钟树结构,从而无缝连接到流程的下一步骤。作为EDI 14.20最重要的革新部分,iCTS将在更多、更先进的设计中大展身手,并给用户提供更加优质的体验。