基于人工智能的 Cadence Cerebrus 如何帮助德州仪器在提高性能的同时减少面积

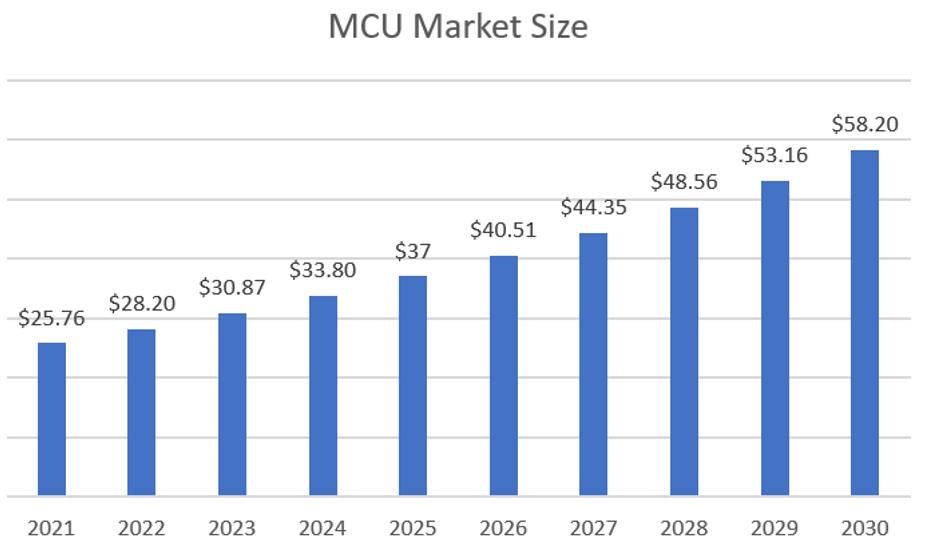

微控制器(MCU)已经成为嵌入式设计的支柱,为各类应用设计提供动力。它们的重要性怎么强调都不为过。预计到 2030 年,MCU 市场将达到惊人的 600 亿美元,使其成为一个高利润的行业。

数据来源:Precedence Research

在当今快节奏的技术世界中,有大量应用程序和多类 MCU 可供选择,每个 MCU 都有自己独特的外设和内存要求。外设和存储器的变化使得芯片设计人员对每个 MCU 的综合及布局布线(PNR)方案进行微调变得颇具挑战。但无需担心,Cadence 将为您提供合适的解决方案。据德州仪器(Texas Instruments, TI)透露,Cadence Cerebrus 技术帮助他们将 PPA 和关键设计面积提升了 4.4%,并将违规路径减少了 26 倍,以及将需要人工完成的时序工程变更顺序(ECO)周期缩短了一周。此外,Cerebrus 显著增强了片上 SoC 平面系统,即使物理边界受限,也能在紧迫的时间内突破架构限制。尽管频率受限,但其依旧在标准单元面积内实现了 7.37% 的性能提升。

SoC 时序收敛挑战

不断增加的密度及不断缩小的芯片尺寸给设计带来了诸多挑战。在深入了解解决方案和结果细节之前,让我们先快速熟悉一下芯片设计人员面临的 SoC 时序收敛挑战。

1

SoC 芯片尺寸受到 I/O 或宏的限制

2

历史过往需求导致 SoC 过于制式化(I/O 或宏布局)

3

续代产品无法探索固定组件的理想布局

4

专利核心和重用 IPs 禁止架构反馈的实现

5

探索坐标最终决定前确认芯片尺寸

6

与 I/O 环、电源增益、布局规划和约束开发相关的并行项目,以及试验期间 RTL 的增量变化

在有限的时间内,同时存在上述问题让时序收敛、综合和 PNR 的完成变得非常困难。这就是 Cadence Cerebrus 脱颖而出的地方,作为基于 AI 的自主学习工具,能为最终用户提供基于预期成本的最佳结果。

解决方案

TI 提到,Cadence Cerebrus 在平面 SoC 显示出卓越的功耗、性能和面积(PPA)改进。平面 SoC 受限制物理边界的宏参数影响,需要在紧凑的时间内突破架构局限性。Cadence Cerebrus 的部署为 TI 提供了独特的解决方案,能解决常规流程无法实现的 PPAS 改进问题。以下是 TI 利用 Cadence Cerebrus 实现其面积和性能改进的一些案例。

案例 1

01

TI 设计了一款采用以下配置的设备,并考虑了与宏和 I/O 相关的布局问题:

● 宏主导的 SoC,总数超过 70 个

● 600 万个实例

● 30+分析视图

● 平面时序收敛

在试验 RTL 的“冷启动”过程中,宏列表完成率为 95% RTL,并在约束条件内完成可接受的时序收敛。共耗时 22 天,面积目标优化 4.2%。该模型文件被用作下一个 RTL 版本的“热启动”输入,面积目标提高了 4.5%,但完成共耗时 18 天。TI 使用 Cerebrus 的“重放”功能,采用最优的“热启动”场景,仅花费 10 小时的运行时间即获得与“热启动”一致的提升!

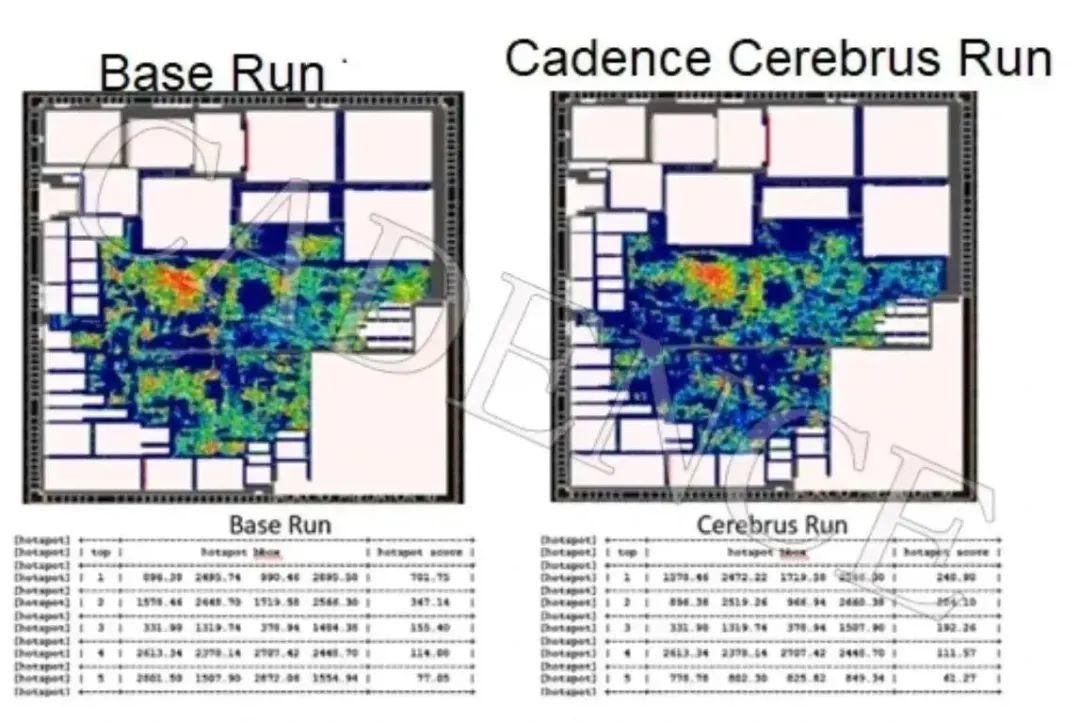

此外,TI 利用 Cadence Cerebrus 实现了利用率的直接提高,密度降低 3.5%,热点减少 3.5%,从而降低了 DRC。此外,具体提升还包括如下方面:

●

后期布线阶段,TNS 减少 3 倍

●

设置违规降低 26 倍,关键 IP 上的 WNS 降低超过 100ps

●

保持违规数量略有增加,但用 TSO 很容易修复

●

WNS 改善将 ECO 周期缩短近 1 周

●

Cerebrus 执行是对逻辑重构相关的关键时序路径进行改进

案例 2:频率推移

02

对 TI 来说,时序和性能是关键指标,因此他们考虑过拥有超过 160 个宏的宏主导 SoC。TI 在设计这款时序关键型 SoC 时部署了 Cadence Cerebrus 以提高性能:

● 平面时序收敛

● 60+的分析视图

● 500 万个实例

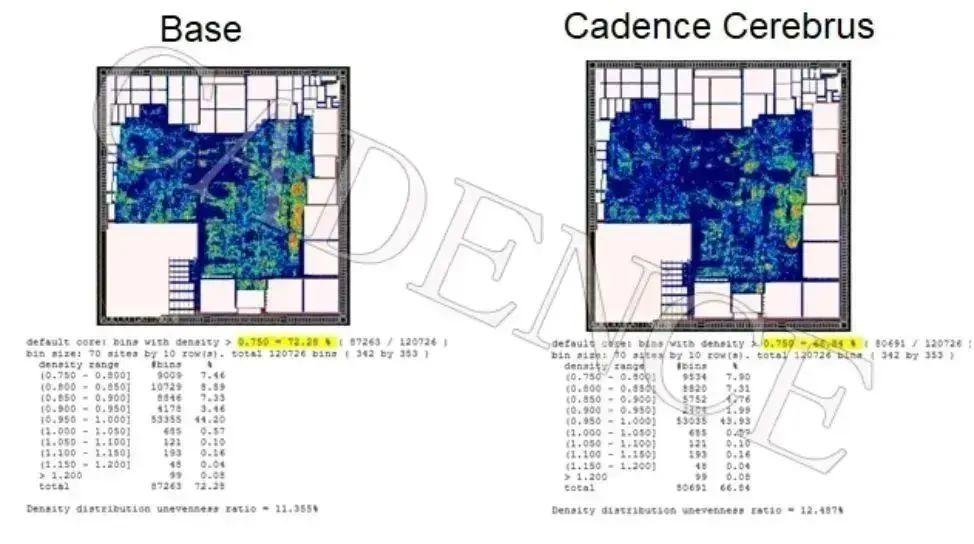

Cadence Cerebrus“冷启动”的初始部署面积目标提升了 8%。TI 设计人员观察到,“基础”和 Cadence Cerebrus 时序都能轻松满足,从而将系统时钟频率提高了 5 MHz。“热启动”设计中,在 5Mhz 频率推移实验中实现了积极的 TNS 偏移,该设计是测试用例 1 大小的两倍。尽管频率提高,TI 设计人员仍能维持 7.37% 的标准单元面积提升。

此外,测试人员还注意到了利用率的直接改善和热点的减少,从而能实现更快的 DRC 收敛。

让 TI 决定采用 Cadence Cerebrus 的关键

●

采用用户定制的流程,并在此基础上生成场景

●

根据场景的成本(PPA 参数函数)来判断这些场景

●

Cadence Cerebrus 能并行运行多个场景,由 AI 引擎来决定是停止、继续,还是进入更多场景

●

这种方法有助于优化流程,并可以降低运行场景的成本

●

它使我们能够根据场景成本计算的设计关键来选择 PPA 指标

●

UI 可以清晰呈现 HTML 中的 PPA 参数和成本改进比例

●

良好的灵活性,工程师可以选择哪怕被丢弃的场景

结论

Cerebrus 在平面 SoC 设计中展示了卓越的 PPAS 改进。平面 SoC 受限制物理边界的宏参数影响,需要在紧凑的时间内突破架构局限性。

测试案例 1

●

PPAS 关键设计面积增加 4.4%。

●

路径违规减少 26 倍,直接缩短时序 ECO 循环一周的工作量。

测试案例 2

●

在大于测试案例 1 两倍大小的设计中,使用“热启动”进行 5Mhz 频率推移实验,TNS 移位为正。

●

尽管存在频率推移,依然能够维持 7.37% 的标准单元面积获益。

●

直接改善热点利用率低的问题,实现快速的 DRC 收敛;“重放”功能则可以节省运行时间。