让CST告诉你小小的缝补电容在EMI中的作用

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。

跨分割,对于低速或者低频信号来说可能影响不大,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下不良影响:

(2)容易使信号之间发生串扰

(3)会引发信号之间的反射

(4)增大电流的环路面积、加大环路电感,使输出的波形容易振荡

(5)增加向空间的辐射干扰,同时容易受到空间磁场的影响

(6)加大与板上的其它电路产生磁场耦合的可能性

(7)环路电感上的高频压降构成共模辐射源,并通过外接电缆产生共模辐射。

缝补电容

缝补电容(stitch cap),在电源层被分割,而又作为参考平面时,就需要这样的电容,给高速信号提供尽可能短的回流路径。一般4对高速差分信号可以共用一个这样的电容,通常在信号跨分割处摆放一个0402或者0603封装的瓷片电容,电容的容值在0.01uF或者是0.1 uF,如果空间允许,可以多添加几个这样的电容,且电容放置在高速信号跨分割区域200mil以内,距离越小越好。

那么这个缝补电容对解决EMI问题有什么帮助呢?

好了老规矩,是时候让CST出场了。我们这篇文章的目的最终是为了对比跨分割信号加不加缝补电容的在EMI上的差别。

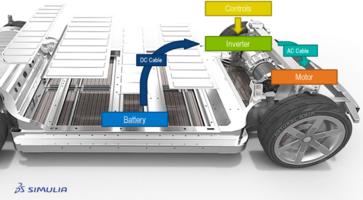

首先找个跨分割的PCB,我这边找的比较简单,如图中原PCB,这边标出了跨分割位置和电流回流路径。

在跨分割区域增加一个离散端口,后面电路仿真时设置一个缝补电容,PCB如图:

增加缝补电容的PCB的磁场分布和表面电流

从图中可以清楚地看到,没有缝补电容时,电流全部从下方的电流回流路径流回去,所以磁场分布随着电流走向的分布从源端通过导线到负载端,然后通过下方的回流路径再流回源端,这边的磁场达到-80dB(A/m)。

而加了缝补电容之后从图中我们看,电流的高频部分走最小阻抗路径,从负载端通过缝补电容流回源端,所以在上方的磁场更强一些,直流部分和低频部分会沿着最小电阻路径通过下方流回到源端,这边的磁场达到-100dB(A/m)。

2.分别在距PCB上方100mm的位置添加Probe,测试电场强度。

仿真结果对比,有缝补电容和没有缝补电容在低频上场强差别不太明显,频率越高,有缝补电容的场强越低,设置差10dB以上。

综上所述:PCB板上跨分割会造成的电流环路面积过大和回路电感过大的问题,会导致信号波形振荡,增加空间的辐射干扰,同时也容易受到外部磁场的干扰。引入缝补电容就可能有效的解决或者优化这些问题。