射频产品设计需要考虑哪些问题?

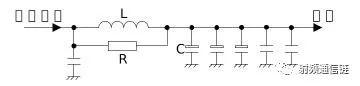

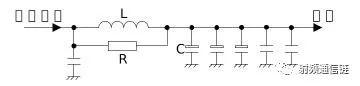

电源处理是射频设计的第一道功课,电源处理不当,有源射频电路将前功尽弃。同接收机一样,浪涌、噪声、DC-DC纹波、共模干扰都不可忽视,由于发射机是大信号,处理难度小于接收机。功放管在整个频率范围内的额定输出功率,考虑到最大输出功率与功放管结温紧密相关,应该有2dB以上的功率余量,如果是非恒包络调制,会存在峰均比,功放的非线性还会恶化ACLR,所以实际的功放输出功率应该在饱和输出功率的基础上再回退若干dB。功放管的输入、输出阻抗随频率变化,使得输出功率一样随频率起伏,为了使输出功率稳定,必须进行闭环控制,最佳闭环控制采用数字APC的方法,通过前向检波,检测输出功率的偏差量,再通过数字衰减,调整激励功率,是输出功率稳定。工作频率越宽,功放的输入、输出匹配网络越复杂,通过多级匹配展宽功放管的工作带宽,只有功放管的输入、输出处于良好的匹配状态,功放管的输出功率才能达到最大,效率才会最低。三阶互调也与匹配网络密切相关,功放管有两种匹配准则:按最佳互调和按最大输出功率,这两种匹配可能不会吻合,需要折中。匹配网络同时也是一种滤波器,滤波器的传递函数有个随频率变化的相位因子,可以改变不同频率失真分量的相位,如果相位相反,则部分互调失真抵消,这就是最佳互调匹配。 效率关系到功耗,手持式采用电池供电,效率影响到电池的持续工作时间。从另一个层面,效率还影响到无用功耗,这部分功耗等于自身发热,使器件温度升高。通常说的输出效率将输出功率与电源功耗相比:η=Pout/PDC×100%,另一个概念是附加效率PAE(Power-Add Efficiency),输出功率扣除了输入功率,是功放的净输出功率,是对效率更准确的描述,PAE=(Pout-Pin)/Pdc×100%。有两种稳定状态:条件稳定和无条件稳定,考虑到功放的工作频率范围宽,温度适应范围从-45~+85℃,条件稳定有潜在的自激危险,必须将功放设计成无条件稳定,即应通过反馈、偏置、匹配将功放牵引到稳定圆内。收发隔离是对收发双工器的要求,当发射的时候,会通过双工器泄露到接收机前端,造成LNA饱和或损坏。设计多大的隔离度合适,一般原则是使射频AGC不起控,避免发射转接收后,因AGC时间常数(检波器输出)较大,射频前端来不及响应,一般TDMA双工器可以做到50dB以上。单纯功放输出的宽带噪声一般不大,当发射机激励功放后,功放输出的宽带噪声会显著增大,为不影响附近工作的其它设备接收机,这个宽带噪声必须限制,通常要求地面设备近端低于-110dBc/Hz,偏离10%fo以远宽带噪声低于-130dBc/H,特殊频段甚至要求更低。 要达到这个指标,除了要限制接收机的输出宽带噪声外,功放本身也需要优化设计。一般功放的总增益应该限制在30dB以下,功放的推动级输出端应该采用调谐滤波器或滤波器组。这样方有可能将输出近端宽带噪声限制在-110dBc/Hz以下。功放具有非线性,输出必然含有谐波,谐波属于无用发射,会干扰附近其它设备接收机的工作,可以当作杂散看待。一般要求手持式谐波低于-50dBc,车载式、机载式谐波低于-70dBc。为降低谐波水平,功放输出端必须级联滤波器,由于带通滤波器的插损太大,一般采用低通滤波器,对于宽频带功放,fH/fL>1,谐波落在工作频段内,所以需要低通滤波器组。A类放大器在P1dB附近的2次谐波大约是-20~-25dBc,饱和输出时谐波更大。AB类放大器由2个A类放大器组成,输入、输出端均有反相巴伦,功放输出的偶数次谐波同相,经过后面的反相巴伦合成后,偶次谐波抵消。如果2个放大器的幅度平衡、相位平衡较好,2次谐波大约-30~-40dBc。相比之下采用AB类放大器,谐波抑制具有优势。经过推挽放大和不平衡-平衡转化,谐波抑制可以提高,因此可以通过功率合成的办法,提高谐波抑制。当fH/fL>>1,比如30~512MHz,频率覆盖达17倍,如果用滤波器来抑制谐波,至少需要含6个滤波器的滤波器组,结构十分复杂,插入损耗也不可小视,如果采用功率合成的方法(涉及到各支路幅度问题),难度会小很多。 功放是发射机的链路延伸,与发射机一样,三阶互调会影响ACLR,使EVM恶化,由于功放的输出功率更大,功率回退较小,非线性更加严重。三阶互调指标主要用于衡量多信道、多载波时,互调分量对系统的干扰程度,任何2个信道都会产生2个三阶互调产物,干扰上、下2个等间隔信道。EVM是接收机解调的保证,EVM恶化太多,会损失解调信噪比,对于恒包络调制,通常功放的EVM<5%,非恒包络调制,为降低ACLR,功放输出功率必须回退几dB,EVM通常较好,<3%。功放的输出驻波比与激励功率有关,当激励为0与满负荷激励时,驻波比相差较大,不能用矢量网络分析仪来测量,应该用通过式功率计进行测量,驻波比一般小于1.5。当功放输出负载开路或短路,输出功率全反射回功放管,与功放管输出电压叠加,使功放管漏极电压加倍或等效短路,可能损坏功放管。为防止功放管损坏,通常降低激励,使输出下降3~10dB,保护功放管,当负载开短路恢复正常后,逐步恢复原激励功率。天线不是纯阻负载,宽带天线的阻抗变化很大,通信系统要求天线的驻波比不大于2.0。当驻波比等于1时,阻抗匹配,输出功率最大;当驻波比为2.0时,阻抗失配,功放的输出功率下降。通常,当采用驻波比为2.0的假负载时,功放输出功率下降值应不大于1dB。 不管是电池供电还是外接直流电源供电,电源电压并非一直保持恒定,当电源电压升高、或下降时,功放输出功率可能会发生变化,特别是恒包络调制,功放工作在饱和状态,电源电压变高,饱和输出功率变大,电源电压变低,饱和输出功率变小。当电源电压在极限电压范围内变化时,功放的输出功率变化不应该超出2dB。除此之外,采用非恒包络调制的波形,EVM还必须达标。当工作温度从最低到最高变化时,手持-25~+60℃,车载-45~+85℃,机载-55~+70℃,功放的输出功率变化不大于±1dB,过温可以进行热保护,允许输出功率降低3dB。在全温范围内、全频率范围内、标准输出阻抗,功放的输出功率应该保持稳定,输出功率变化不大于±1dB。功耗与效率紧密相关,窄带功放的输出效率几乎等于最大输出效率,为了扩展带宽,宽带功放几乎处于匹配状态,效率大大下降,如何提高输出效率与如何展宽功放的带宽都是功放设计的最大难题。对于TDMA体制工作的设备,当处于接收状态时,功放应该关闭,防止功放输出噪声干扰接收。由于功放断电/上电时间达ms级,为适应设备收发转换us级的需要,功放不能完全断电,功放管只能处于待机状态,加漏压,只关闭栅压。这样流经功放管漏极的电流几乎为零,起到降低功耗的目的,而且上电很快。除了末级功放管外,推动级放大器也一样需要待机,进一步降低功耗,降低噪声。功放的收发转换时间不是双工器的T/R开关转换时间,而是从功放的栅极打开开始,到输出功率上升到90%的时间(保持激励),同样从功放的栅极关闭开始,到输出功率下降到10%的时间(保持激励)是发收转换时间。功放本身应该不存在杂散问题,当功放的电源部分设计不良,出现内部浪涌或较大的纹波,电源可能会影响功放,产生电源杂散、开关杂散,功放工作期间,或收发转换期间,功放不应出现自激、瞬时指标异常、短时输出功率变化太大,等不稳定现象。功放管的管芯温度最高,必须通过温度传感器实时采集功放管的壳温,由处理器判断是否过温,是否要进行过温保护。正向、反相功率检测用于功率闭环控制,稳定输出功率。反相功率除以正向功率就是驻波比,处理器可以由此判断功放负载是否异常。电源的最大负载能力是有限的,最大工作电流不能超过电源最大电流值,开机冲击电流会产生开机浪涌,也不能太大。功放的电源必须经过相应处理,退耦、滤波、抑制浪涌,提高电磁兼容能力。滤波电容越大,电源越平滑,但开机冲击电流也越大,单个滤波电容的ESR较大,频繁的充放电使电容发热,多个电容并联,使ESR成倍降低,发热大大减小,延长了电容的使用寿命。功放是设备功耗最大的部件,电源的充放电、浪涌容易引起电源欠阻尼振荡,需要大功率电阻增大阻尼,抑制振荡。通常将大功率电阻与磁芯电感并联,对于直流,电阻被电感短路,不产生压降,对于交流,电阻被接入,吸收振荡。设备采用突发通信,发、收工作比不高,电源电流也是脉冲,如果采用电容存储的方法,平滑电流,将大大降低输入峰值电流,类似于脉冲功放。这种脉冲电源储能电容不能直接并联在电源线上,需要单独设计电流源充电,限制充电电流。功放的电源电流很大,电压较高,极易干扰小信号射频和低频电路,原则上功放按照信号流向布局,推动级与末级输出采用空间隔离,防止自激。电源输入口应该在末级功放管一侧,所有小信号、控制电流电路应该远离总电源滤波、退耦,远离末级放大器。采用金属壳屏蔽的功放结构,应该实现仿真、计算腔体的谐振频率,谐振频率必须大于最高工作频率的2倍以上,以留出足够的安全余量。军用通信设备通常工作于很宽的射频频段,射频低端频率较低,时钟的谐波极易落入工作频段内,成为无法避开的干扰。通常,晶体振荡器直接输出的都是切顶正弦,谐波十分丰富,可以通过低通滤波器将切顶正弦(准方波)过滤成正弦。为降低谐波干扰,宽带设备使用的频率参考源采用正弦波形,并通过BPF或LPF抑制时钟谐波,使谐波低于-40dBc(切顶正弦的谐波更高),即便在这种情况下,时钟的高次谐波泄漏到射频通道仍然可以达到-80~-100dBm,远高于接收灵敏度,使谐波频率点不能正常使用。由于晶振电路本身也会泄漏高次谐波,当后级滤波器对谐波的抑制达到一定程度,再增大抑制就几乎没什么改善。另外,由于阻抗失配、电路寄生参数的影响,方波容易产生过冲和振铃,使时钟的过零点产生偏移,恶化相位噪声。相反,正弦波不存在过冲和振铃问题,所以正弦波的相位噪声好于方波。这个结论在电路噪声较小的情况下成立,当电路噪声较大,叠加在正弦电压上,同样会引起过零点的偏移,而方波的偏移量就明显小于正弦波。由于数字单元的脉冲噪声很大,而射频单元的噪声相对较小,故将时钟放在射频部分是一种更合理的做法。 窄带通信为降低电路复杂度、降低成本,时钟通常采用方波。如果使用多时钟,原则上各时钟应该同源,即保持同步。不同于雷达,通信设备各时钟之间不一定有很严格的相位关系,故有的设备多时钟之间是异步的。需要注意的是,时钟越多,谐波频点也越多,干扰也就越严重。设备需要很多路时钟,ADC、DAC、FPGA、ARM、DSP、PLL等,原则上时钟由射频部分产生,射频部分有几路本振就应有几路时钟,对数字基带部分可给出1~2路时钟,ADC和DAC最重要,应优先使用。如果晶振的输出电平较低,应先放大后分配。有另一种做法,由数字基带部分产生时钟,在FPGA里将时钟分作多路,共各部分使用,由于FPGA是数字器件,干扰严重,相位抖动也很大,用这种简单方法得到的时钟,基本指标会较。功耗在整个设备设计过程中都不可轻视,是需求严格限制的技术要求,功耗大还会产生过多热量,使设备温度升高,方案阶段必须优先选择电路简单、功耗低的方案,器件选型也必须优先选择功耗的器件。 功放是设备的发热大户,功放的结构、末级功放管的安装位置影响到散热效果,需要通过有限元热仿真来确定最佳方案。设备对热最敏感的单元、模块应远离功放的安装位置。机内自检BIT(Built-in Test)是GJB要求的功能,完成六性规定的可测性,同时也辅助维修性对故障部位的判断。机内自检分为开机自检、周期自检、按需自检。自检应完成对链路所有单元的检测,故障隔离到模块。为此,每块PCB、每个功能单元的输入输出均需要检测,PLL的锁定指示需要检测,电源是否正常需要检测。自检需要激励源,发射机自身可以产生调制射频信号,接收机需要增加辅助信号源,可以用晶振的谐波或者FPGA输出方波的谐波,通过检测输入、输出功率可以大致判断模块链路是否正常,若将发射机与接收机变环,接收机分析解调数据,计算EVM,可得出链路是否正常,发射、接收信号质量是否正常,间接知道本振是否锁定。1)开机自检:开机上电后,程序加载完成,进入自检模式,处理器采集所有功能模块的状态,异常者以故障标示,并上报。2)周期自检:处理器定时切换电路功能,进入自检模式,采集所有功能模块的状态,异常者以故障标示,并上报。 3)按需自检:当用户或上位机下达单元自检命令后,处理器完成当前工作,切换电路功能,进入自检模式,处理器采集所有功能模块的状态,异常者以故障标示,并上报。EMI包含传导CE(Conducted Emission)和辐射RE(Radiated Emission)。CE的频谱范围25Hz~40GHz,RE的频谱范围25Hz~40GHz。EMS包含CS传导敏感度和RS辐射敏感度,CS:ESD,快速脉冲群,浪涌,注入电流,电源跌落;RS:强辐射电磁场。

版权声明:射频学堂原创或者转载的内容,其版权皆归原作者所有,其观点仅代表作者个人,射频学堂仅用于知识分享。如需转载或者引用,请与原作者联系。射频学堂转述网络文章,皆著名来源和作者,不可溯源文章除外,如有异议,请与我们联系。 著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2023-12-20

最近编辑:4月前