电平转换,搞硬件“看家护院”必备良药

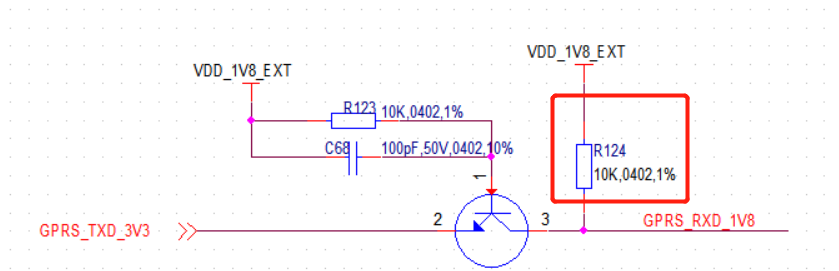

E端输出低电平时(0V) ,NPN三极管导通,C端输出是低电平(0V); E端输出高电平时(3.3V),NPN三极管截止,C端输出被拉高至高电平(1.8V); E端输出高阻时(OC) ,NPN三极管截止,C端输出是高电平(1.8V);

R124电阻会影响信号边沿的陡峭程度; 电路可用在信号通讯速率不高的场合; 单向通讯;

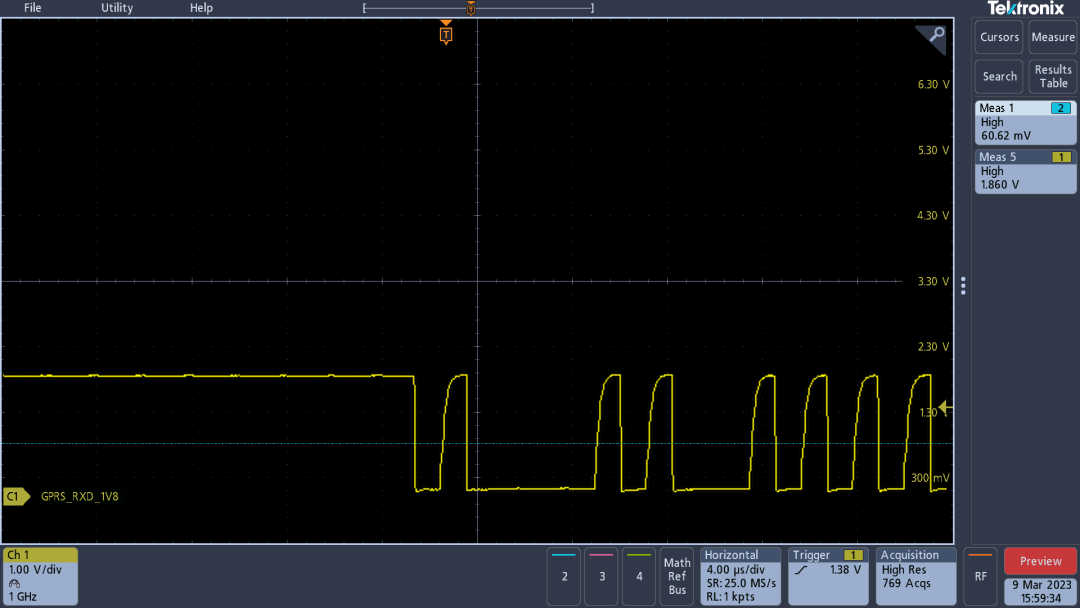

图 2 R124=10kΩ

登录后免费查看全文

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2023-06-08

最近编辑:1年前

还没有评论

相关推荐

最新文章

热门文章