一个板级工程师整了小半年芯片后的感悟(上)

由于工作的变化,芯片设计的学习暂时会告一段落了。以后有缘再继续。

回想一下,从刚开始的迷茫,到现在一只脚踏入门,中间过程还是值得记录一下。

我是怎么开始的呢?

首先呢,在腾讯课堂上,有一门chris的芯片课程,价格很亲民,百元左右。

果断入手,挑其中的低噪放章节看了一下。

看下来的感觉呢,软件操作和ADS差不多,仿真器呢,也类似。

但是,电路呢,着实是看不懂。

板级上的低噪放,可能就只有一个器件被称为管子。但是芯片级则满屏都是管子。

然后我怎么办了呢?

虽然我不是芯片专业,但我也知道razavi。所以我就在搜索引擎上输入razavi。

最后找到了网友放在B站上的razavi的教学视频,主要讲微电子基础。

接着,就开始踏踏实实的看razavi的视频。

感慨于老R的教学水平,不仅让知其然,而且让知其所以然。一路听下来,收获颇丰,也作了很多总结。

接着呢?

看完视频教程后,再回过头去看chris课程上的LNA电路。发现这会,电路能看懂个七七八八了,但是还是不知道怎么设计。

再然后呢?

然后去看Razavi的射频微电子了。因为要做VCO,所以就从振荡器这一章开始。

从底层理论上来讲,板级的和芯片级的一样。

一种是基于反馈理论,即巴克豪森准则;另一种是基于负阻理论,即要用有源器件产生一个负阻,来抵消谐振器中的阻性消耗。

在Razavi的射频微电子中,讲了三种类型的振荡器。

一种是ring振荡器,书中讲该种架构,工作频率不会太高,因为我要设计的VCO在6GHz左右,所以就没有深看。

还有一种,是Colpitts振荡器。不过因为其起振条件相对于后面一种振荡器要严苛一些,再加上它不是天然的差分结构。要使用的话,还得再添加额外架构,所以用的也不多。因此也没有深看。

第三种,就是交叉耦合振荡器,起振条件相对宽松,天然就是差分电路,着重看了这种架构的原理。

再接着呢?

razavi的振荡器部分看完,在结尾处有振荡器的大概设计步骤。但是,没有讲是怎么选管子的尺寸。

找资料的过程中,发现gmid方法。

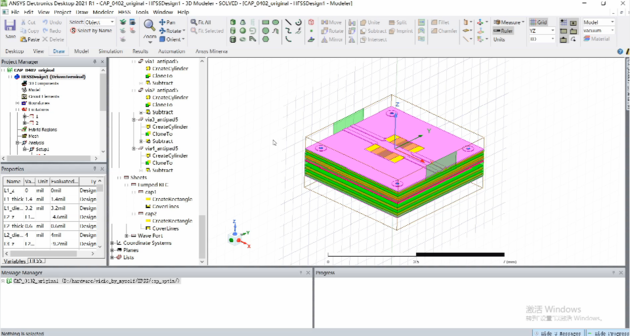

再看chris教程里也讲解了gmid曲线的具体绘制方法,学着做了一遍,把工艺中的NMOS和PMOS的相关曲线给扫描出来了。

又在B站上找到一位台湾老师讲的,用gmid方法设计运放的视频。

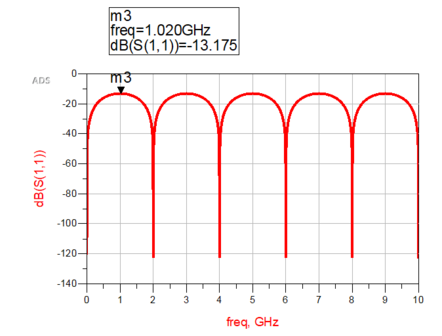

看完以后,结合书中的设计步骤,再用gmid方法选择管子的尺寸。然后到virtuoso中搭建原理图进行仿真。仿真结果振荡,但频率差点,于是又微调了一下参数。

再然后呢?

单点振荡器仿出来了,就想接着仿VCO。

还是接着看Razavi的书,包括射频微电子和CMOS集成电路设计。

虽然书中有讲解,但是看完后,还是一头雾水,不知道怎么具体操作。

看B站上的优质教学视频基本都是从油管搬运来的。于是就翻 墙去找资料。

还真找到一个视频,关于VCO的,视频的讲解者,是一个很资深的芯片设计工程师。

看完这个视频后,顿悟了,原来是这样啊!

再回头看razavi的书,发现能看懂了。

于是开始在virtuoso上搭原理图,稍稍微调,出功能了。。

不过,只用变容管进行了调谐,一是因为对相噪要求不高,牺牲少许相噪后得到的调谐范围已完全能满足我的要求;二是,加上离散调谐后,发现相噪恶化严重,也就是说,加上的离散电容显著恶化了谐振器的Q值。

不过,商用的宽调谐的VCO都是离散调谐和变容管调谐相结合的,所以我肯定没找着提升Q值的方法。以后有需要,再深入。

再再接着呢?

VCO仿出来后,又仿真了一下工艺角。发现频率漂的厉害,不能忍。

所以就想着用PLL吧。

因为PLL好的带内相噪,对系统指标是有改善的,而且可以保证高低温下的频率基本保持不变。

所以我的设计目标转向设计一个PLL。