2.5D/3D芯片-封装-系统协同仿真技术研究

本文原刊载于《电子与封装》2021年10月刊“微系统与先进封装技术”专题

作者:褚正浩 张书强 候明刚

摘要:2.5D/3D 芯片包含interposer/硅穿孔(Through Silicon Via,TSV)等复杂结构,通过多物理场仿真可以提前对2.5D/3D芯片的设计进行信号完整性 (Signal Integrity, SI) 、电源完整性(Power Integrity, PI)及可靠性优化。本文总结了目前2.5D/3D芯片仿真进展与挑战,介绍了基于芯片模型的Ansys 芯片-封装-系统多物理场协同仿真方法,阐述了如何模拟芯片在真实工况下,达到优化芯片信号完整性、电源完整性,优化散热方式,提高结构可靠性的设计目标,并进行电热耦合、热应力耦合分析,指出了仿真技术的未来发展方向。

关键词:2.5D/3D芯片;芯片-封装-系统;多物理场;仿真;Ansys

1

引言

随着半导体工艺节点进入到7nm/5nm之后,半导体芯片的工艺难度逐渐加大,研发及制造成本也显著增加,半导体行业逐渐步入后摩尔时代,在技术发展方向上半导体产品出现了2.5D/3D IC,通过先进封装(Interposer、TSV)的方案实现Die-to-Die的互连。先进封装的设计方案可以进一步缩小器件互连的距离,不仅电性能能够得到提高,还可实现多样化集成,包括通过异质集成的方法实现多种形式的微系统。但设计复杂度的提高,对设计方法,包括仿真方法也提出了很大的挑战,包括电磁、热、结构以及多物理场耦合分析。并且2.5D/3D芯片目前的主要应用场景包括人工智能/网络通信等,其典型功耗可能高达300W,所以在实际工作过程中,功耗及散热问题,以及热应力形变等问题非常突出,设计面临的挑战包括,如何有效的优化芯片功耗,保证信号通道的传输速率,保证系统散热能力,确保热/结构可靠性能力,如何通过仿真手段在初期对设计方案进行筛选和优化,尤其是针对2.5D/3D芯片封装的仿真方法和流程,也是目前业界的研究热点,内容包括Interposer/TSV等结构的性能优化,芯片与封装的联合仿真,电热耦合仿真等。本文主要介绍了 2.5D/3D芯片封装的发展趋势及其对传统仿真方法流程的挑战,并通过经验总结讨论了针对的2.5D/3D芯片的芯片-封装-系统协同多物理场仿真方法。

2

2.5D/3D芯片仿真设计挑战

2.1

2.5D/3D芯片先进封装发展趋势

半导体行业最著名的一条经验当属摩尔定律了,即集成电路上可容纳的晶体管数目,约每隔18个月便增加一倍。摩尔定律在过去的50年成为半导体行业一直遵循的准则,准确预言了整个行业的技术发展。但半导体的工艺呈指数增长的状态不可能无穷无尽的持续下去,尤其是近年来,在2017年,半导体工艺节点进入7nm之后,种种物理限制使得工艺改进带来的效益逐渐降低,是未来在2-3nm的工艺节点上,导线宽度只有大约几个原子的大小,量子力学的不确定原理使得晶体管不再可靠,摩尔定律将很难维持下去。但信息交互和传递的需求却对半导体芯片提出了更高的要求,2016年底全球移动数据流量达到每月 7.2 EB(1 EB=260Bit),这个数字到 2021 年会超过每个月49 EB[11]。在2005年,国际半导体技术路线图组织(ITRS)提出了“后摩尔定律”,以多重技术创新应用向前发展,以应对和满足未来市场的需求。系统级芯片(system on chip, SoC)与系统级封装 (system in package,SiP)都是实现更高性能,更低成本的方式[2],其中以三维立体封装为代表的先进封装技术将是后摩尔时代的核心驱动力之一,当前有多种3D堆叠技术,包括Bond wire, Flip chip及TSV等 [7] 。通过先进封装的技术,越来越多的2.5D/3D芯片相继面世,3D封装和 2.5D封装之间的基本区别在于,2.5D 封装在Interposer上并排互连芯片,而 3D 互连层将芯片进行堆叠,即互连结构在彼此的顶部[16]。业界无论从设计者还是晶圆厂都在大力发展2.5D/3D封装的相关技术。

TSMC是全球领先的晶圆代工厂,也是目前晶圆级先进封装技术的代表和推动者,最早在2015年,其在苹果的A9处理器上已经使用了InFo封装技术,TSMC版A9处理器的续航能力明显强出三星代工的芯片,从此TSMC不断增强和巩固其在先进封装的优势技术地位,其认为芯片的3D互连将是未来的重要发展趋势,能够有效提升系统效能、缩小芯片面积并整合不同功能。图1展示了TSMC主要的先进封装形式,目前TSMC已经将SoIC((System-on-Integrated-Chips) 、CoWoS (Chip On Wafer on Substrate)、InFO(Integrated Fan out)、CoW(Chip On Wafer)、WoW(Wafer on Wafer)等先进封装技术平台加以整合,统一命名为“TSMC 3DFabric”。通过此平台,TSMC将提供芯片互连解决方案,满足用户在整合数字芯片、高带宽存储芯片及特殊工艺芯片方面的需求。

图1 TSMC先进封装解决方案[17]

英特尔也不断推动其在先进封装方法上的进步,推出了3D Foveros封装技术、横向拼接Co-EMIB(嵌入式多芯片互连桥接)等技术,EMIB是一个复杂多层薄硅片,可以在相邻芯片间传输大量数据,通过EMIB可实现处理器、图形卡、内存及其它多个芯片间的通信。目前英特尔还介绍了新的先进封装技术——“混合结合(Hybrid bonding)”,能够实现10um及以下的凸点间距,较Fovreros封装的25~50um凸点间距有了明显缩小,并且优化了芯片的互连密度、带宽和功率表现,进一步提升芯片系统的计算效能。

无论是哪种先进封装技术,其目的都是为了缩短互连长度,尤其是的互连长度,以减少寄生效应的影响,从而提升系统的性能,并且降低系统的整体功耗,尤其是对于人工智能(Artificial Intelligence,AI)等芯片类型,2.5D封装技术如CoWoS已经得到了广泛的应用。

图2 CoWoS 架构[9]

图2展示了CoWoS的主要结构,通过CoWoS,设计者可以实现1* SoC 4*高带宽内存(High Band Memory,HBM)的芯片架构,极大的扩展了SoC与HBM之间的带宽,尤其是Interposer/TSV等互连结构的引入,帮助设计者更加有效的提升了互连性能。其中Interposer通常基于65nm制造工艺或类似工艺制造,可以用于连接SoC与HBM,TSV可以将芯片在高度方向上进行互连,实现了贯穿整个芯片厚度的电气连接,更开辟了芯片上下表面之间的最短通路,3D存储芯片封装也会在将来大量的用到TSV。先进封装技术也进一步推动了异质异构集成以及Chiplets的发展,因为模具材料的差异,一些芯片组逻辑上属于一起形成系统或子系统的不能集成到单个芯片中,硅和砷化镓就是这种情况[15],Chiplets就像拼图一样,可以将多种器件及晶圆组合在一起,比如微机电系统 (Micro-Electro-Mechanical System,MEMS),数字,射频等器件,形成一个集传感、通信、处理、执行、能源管理为一体的微系统,实现了多样化的产品应用。

2.2

2.5D/3D芯片的仿真需求

2.5D/3D芯片中TSV通常与再布线层(Redistribution Layer,RDL)层结合使用 [10],通过TSV 的互连可实现更小的外形尺寸、更低的功耗和更高的信号传输速度[4],极大提高了芯片互连的性能,但设计难度也很大,包括走线设计,电源稳定性,电磁干扰、热结构可靠性等,传统的仿真方法也面临着极大的挑战。

大尺度变化对高速信号通道仿真

求解能力的挑战

当信号的工作速度较低时,封装和印刷电路板(Printed Circuit Board,PCB)中由键合线、引线、框架、焊球等构成的互连结构只用通过抽取寄生的集总参数即可评估其性能,随着频率的升高,设计者必须通过3D全波的电磁仿真方法抽取S参数等结果进行分析。在当前的2.5D/3D芯片中,高速通道类型较多,如56Gbps的Serdes接口, HBM总线接口等。仿真抽取这些结构通道的难点在于,仿真对象的尺寸结构跨度过大,Interposer上的结构尺寸特征较小,会低至um级,但芯片及封装基板的设计尺寸则大都在mm级,所以仿真工具必须有能力在保证精细结构建模的同时具备大规模模型的求解能力。

高功率对电源稳定性及散热的仿真挑战

2.5D/3D 芯片的典型应用是AI/高性能计算(High Performance Computing,HPC)等芯片类型,芯片本身工作功率就很高,工作电流可达200A,设计者必须仔细设计Interposer/基板上的电源结构,保证较小的直流压降、电流密度和交流电源噪声。芯片中的电源/地管脚为信号管脚提供信号回流路径,电源/地管脚上的寄生参数、管脚数目和位置分布,直接影响到信号管脚的特征阻抗和信号质量。传统的仿真方法主要评估结构的无源特性,如电流回路的R/L等指标,但在如此大的功耗下,设计者必须在瞬态确认电压瞬态噪声是否能够达标,其次还需要模拟多种芯片工况反转所导致的电压降。并且Interposer等结构使得芯片集成度更高,功率密度的增加使得芯片的散热设计成为极大挑战,但传统的热仿真软件很难处理Interposer上的精细结构。

芯片/封装的协同仿真需求

在目前的设计流程中,芯片、Interposer、封装、系统的工作人员独立完成设计任务,导致最后在系统集成时,虽然每个器件都有已经经过仔细设计,但因为实际应用环境与前期设计环境的参数差异导致系统工作无法达到预期。尤其是Interposer和封装的设计需要考虑多种因素,包括工艺、结构、材料、散热等,如何把握Interposer/封装结构的各种寄生效应成为制约设计成功的关键因素,准确地抽取封装结构的电气性能是非常关键而重要的一步。一方面芯片设计部门和系统设计部门会要求封装部门提供封装的电性能参数,如RLCG或S参数模型,结合Interposer/封装寄生效应进行系统分析;另一方面Interposer/封装设计人员也需要根据芯片和系统分析的结果进行设计优化,对寄生效应做出必要的补偿,改善设计性能,从而最大限度地减少设计迭代,在有限的设计周期内完成高质量的设计。但如果将完整的设计文件统一到同一工程中进行建模仿真,仿真求解效率较低,必须寻找更有效的协同仿真方法才能满足工程设计要求。

多物理场仿真设计的挑战

芯片功能越来越强大,对电流的需求也越来越大。大电流产生的热量如果不及时处理,芯片结温过高,会导致芯片工作异常。温升不只发生在芯片处[14],也会在焊点处,长时间的热应力也会使芯片和封装上的互连结构变形熔断,甚至烧毁芯片。这些物理现象的产生是由多个物理域互相耦合作用的结果,单一场求解器无法准确模拟实际的芯片工作状态,设计者在进行仿真设计时,必须将单一物理场求解器结合起来,进行多物理场协同分析,才能够准确仿真实际的工作状态及环境,考虑电、热、力之间的相互耦合,通过多物理场仿真优化设计方案将芯片产生的热量通过封装及时散出去,并不造成应力破坏,同时达到芯片电、热和应力的设计目标。

3

2.5D/3D芯片的仿真方法

为应对2.5D/3D芯片不断增长的仿真需求,各大EDA公司也纷纷加大投入,尤其是近年来高性能计算机技术和EDA软件的飞速发展,使得仿真复杂的2.5D/3D芯片的物理现象提供了可能,并且在目前的EDA仿真发展过程,设计者和EDA厂商都更加注重Chip Package System协同的多物理场仿真技术。传统的流程中,Chip/Package/System一般单独设计,在最终的系统集成后,才能够确认系统性能是否达标,集成度的提高使得设计余量越来越小,必须准确分配设计裕量才能提高设计成功的概率,所以芯片-封装-系统(Chip-Package-System,CPS)协同的仿真方法目前使用的越来越多。

EDA厂商CPS协同仿真方案对比

EDA 行业存在高度垄断,市场上能够提供Chip Package System协同分析的方案的EDA厂商只有Ansys/Cadence/Mentor/Synopsys等几家头部企业,当前国家大力发展芯片产业也给中小 EDA 公司带来了新的机遇,但是国内EDA 软件性能和主流的EDA工具具备一定差距,故本文以国际EDA软件为主要研究对像,EDA厂商根据各自的工具特点,在CPS仿真布局上有明显不同, Cadence/Synopsys主要特点是IC设计流程较全面,但Cadence除IC设计流程外,也提供了封装/PCB的系统SIPI/热仿真方案。Ansys的产品线全部布局在仿真验证方向上,仿真技术完全涵盖了芯片,封装及系统仿真领域,以及半导体/电磁/热/结构的物理场仿真,是目前业界功能最全的CPS 多物理场仿真平台,故本文主要基于Ansys的仿真平台进行了CPS 多物理场协同仿真方法的研究。

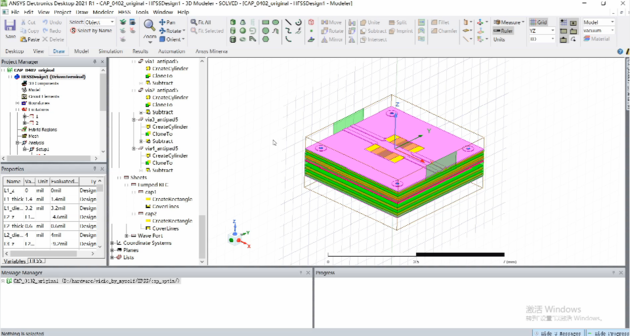

Ansys CPS 多物理仿真方法

目前业界芯片的设计工具类型/设计方法与封装/PCB设计工具/设计环境有着较大不同,所以在Ansys CPS仿真流程,其特点在于通过芯片电源模型(Chip Power Model,CPM)/芯片信号模型(Chip Signal Model,CSM)/芯片热模型(Chip Thermal model,CTM)等模型作为交互基础,将芯片、封装、PCB及系统在同一平台,通过模型互连的方式进行对2.5D/3D 芯片的SI/PI/热等指标进行准确分析。

图3 Ansys CPS仿真协同图

此流程中首先会通过Ansys-Apache产品仿真得到芯片的CPM,CSM,CTM分别用于PI/SI/热分析,其次再利用Ansys的电磁、热、结构等产品进行多物理场协同仿真。

CPS SI仿真流程

典型的SI仿真流程分析分为无源通道优化和有源链路仿真两部分,有源链路遇到的主要问题包括:

预加重设置

均衡设置

无源链路需要考虑和优化的问题包括:

高频衰减

信号串扰

趋肤效应

表面粗糙度

CPS SI的仿真流程图如下,在此流程中,设计者输入了EDA设计文件,材料叠层信息,芯片模型等,通过仿真得到信号通道的无源电磁模型,优化其无源传输能力,并进行瞬态电路分析,SSN仿真分析,得到系统的眼图、瞬态波形,从而评估系统的性能是否达标。

图4 CPS SI仿真流程

而在仿真过程中,准确地抽取互连结构的电气性能是非常关键而重要的一步,Interposer/TSV/基板的无源性能抽取将会极大的影响仿真精度。Ansys仿真工具可直接导入GDS等设计文件,根据设计文件和TSV抽取的要求,按如下流程进行分析。

图5 GDS电磁抽取流程

TSV 在通孔周围有一层薄绝缘层,会带来寄生电容的影响 [20] ,且TSV通道的高频损耗,会降低信号的传输性能 [6] 。对于TSV等单独结构,目前通常的做法是通过Q3D等直接抽取出对应的RLC等效电路,以评估其性能,也可能以使用SIwave-CPA等快速工具进行封装基板仿真,抽取相应的RLGC寄生参数,比如所有Bump上的电感值,进行设计指标优化。

而对于Interposer/TSV等整体结构,可使用HFSS 全波3D求解器得到高精度的S参数模型。HFSS是业界3D电磁仿真软件的标杆,其仿真精度得到了广大用户的认可,其在最新版本也引入了专门求解IC Model求解模式用于先进封装的仿真,尤其是针对Serdes通道的优化。HBM则是Interposer仿真的另一难点,HBM相对于传统DDRx设计来说有更高的带宽和功耗效率,时延很低,占用面积小的特点。如果采用相似的带宽和存储大小的情况下,GDDR6的PCB占用面积是HBM2的6倍,功耗消耗多3倍,芯片设计面积接近2倍,HBM的优势比较明显。但是HBM设计实施却很困难,除了满足严苛的interposer设计规则及信号完整性规则外,还必须考虑高位宽(1024 bits或2048 bits)同步开关噪声问题。Ansys通过CSM工具可针对HBM进行高速的同步开关噪声(Simultaneous Switch Noise, SSN)分析,在此过程中,CSM首先基于GDS提取信号走线及电源平面的RLC,其次联合芯片的IBIS/Spice模型进行SSN分析,图6为Iluvatar通过CSM进行HBM仿真得到眼图。

图6 HBM 仿真报告[3]

如果用户想提高SSN的仿真精度,传统的IBIS模型由于对信号电源之间的耦合描述不够精确,所以无法满足SSN的要求,而Spice模型对DDR并行系统而言,仿真效率极低。Ansys可以从芯片版图中抽取出CSM模型,CSM模型描述芯片内部信号与供电网络之间的耦合关系,且提供了spice级的仿真精度,可以在保证精度的前提下提高SSN仿真效率。

CPS PI仿真流程

对于电源来说,稳定、干净的供电电源是芯片正常工作的基础条件。理想的电源是恒定电平的电压源,但实际上,由电源-地走线及平面、去耦电容等构成的电源分布网络(PDN),由于存在寄生参数,这样当芯片电流流经电源分布网络时,就会造成一定的直流压降和交流噪声,尤其是对于交流噪声,设计者需仔细设计电源的去耦网络,使得电压平稳。

图7 分布式PDN网络

上图显示了一个完整电源去耦网络去耦能力在频域上的分布,芯片、封装和PCB都对电源噪声有贡献,所以必须进行从电源至地的系统级优化[8]。通常Mhz级别的去耦由板上的Bulk电容或陶瓷电容完成,百Mhz频段的去耦由封装完成,Ghz以上的高频去耦则由芯片内部去耦。对于完整的CPS 电源分析,设计者首先要进行直流压降分析,其次将PCB、封装、Interposer及芯片的去耦信息综合后得到全频段的阻抗参数,用于电源网络的频域分析,其中PCB/Package的去耦信息会通过设计文件由HFSS抽取,Interposer的阻抗可以由CSM抽取,即使很小的 TSV 电感也会导致高PDN 阻抗的尖峰[5],Chip的去耦信息则会由下文提到的CPM提供,最终在电路工具仿真工具中进行综合。图8展示了整体的分析流程。

图8 CPS PI仿真流程

其中,直流压降的分析主要通过SIwave完成,但对于大部分2.5D/3D 芯片而言,其单一电源网络的管脚数量可多至上千,所以传统直流压降分析流程中,将电流均分至所有电源管脚上的方法偏理想,在目前的仿真流程,设计者可以从Chip 的压降仿真结果中获取得到精确的电流信息,将每个管脚上的实际电流加载至封装基板上进行分析,以提高直流压降的仿真精度。

其次,对于交流抽取,封装基板可使用HFSS抽取,而对于Interposer而言,其细节结构较多,可用CSM进行RLC寄生参数的抽取,也可以直接将Interposer的设计文件直接加载至Redhawk中进行联合的动态压降分析,Ansys在Redhawk工具下面专门开发了一个3DIC小工具用于该数据互联 [1] 。

CPS电源仿真的另一内容则是电源的瞬态分析,因为CPM提供工作时的变化电流曲线,所以在电路工具中通过瞬态分析可以直接得到芯片工作时电源管脚上的瞬态噪声,使得仿真结果更加易于设计评估。

CPM的全称是Chip Power Model,由Ansys的半导体旗舰产品RedHawk提取。CPM描述了芯片内的电源传输网络,可以精确地模拟芯片从直流到多GHz的各种频率范围内的电响应,从而实现系统级电源完整性设计的分析、诊断和优化。

CPM模型包含两部分信息,一部分是芯片内的无源去耦信息,包括芯片上电源栅格的RLC寄生参数,负载电容等,端口一般位于C4 Bump或Pad上,另一部分是芯片在不同工况下的电流负载曲线,最终以Spice模型的形式体现出来。

Interposer的压降可以多达数十mv [13] ,所以需要将芯片级的CPM模型,Interposer的设计数据以及封装的模型准确无误的连接起来后,采用Redhawk的动态压降分析功能进行相应的PI仿真分析。通过仿真分析结果可得到 “芯片 CPM模型 Interposer模型 封装模型” 的动态压降仿真结果,图9所示的是某芯片动态压降仿真结果,可以非常清晰的知道芯片设计上面各个不同区域的压降分布情况,便于后端与封装设计同事进行设计优化调整。

图9 3D 芯片CPM Interposer电源的动态仿真结果[1]

除通过传统的CPM模型进行电源通道的瞬态分析外,Ansys还引入了一个新的工具CMA用于电源通道的全频段分析,Ansys CMA是芯片电源模型CPM的补充工具。在芯片设计早期,通过CMA可以实现在没有实际物理设计情况下产生早期CPM用来对早期电源分配网络的设计进行优化。在芯片设计后期,通过RedHawk工具抽取实际物理设计的CPM,并通过CMA进行中低频噪声调制,可以实现全频段芯片-Interposer-封装-系统电源网络仿真分析。

通过CMA在设计初期产生随机芯片电源模型

通过输入一些早期芯片规格信息,比如参考芯片规划阶段的规格书上定义的芯片操作频率以及对应的电流幅值,结合芯片片上电源网络寄生RC参数或者导入之前版本类似制程和规模大小芯片的片上RC参数,即可通过CMA将两者结合起来产生早期随机芯片电源模型CPM。

另外,通过和Ansys前端功耗分析工具PowerArtist结合也可以产生早期芯片电源模型,且模型更加接近后端实际物理模型。PowerArtist可以实现长激励向量快速功耗扫描,产生随着时间变化的功耗曲线,该曲线可以和CMA无缝链接并产生早期芯片电源模型,图10展示了PowerArtist的调制过程。

图10 结合PowerArtist功耗扫描曲线产生早期CPM

芯片电源模型CPM拓展和分析

在2.5D/3D芯片设计后期,基于物理设计产生的精确芯片电源模型CPM可以直接导入CMA工具,图11展示了CMA工具进行芯片、封装、系统协同仿真的流程,CMA工具提供手动调制和基于功耗扫描曲线或测试波形两种调试模式。基于手动的调制模式,只需要手动输入芯片操作的典型场景,比如芯片上电过程中开始的静止模式下功耗,上电时间以及芯片上电完成时功耗,即可结合芯片正常操作模式下的芯片电源模型CPM进行调制出该典型场景模式下的拓展CPM模型,进行芯片-封装-系统全频段电源网络仿真。基于功耗扫描曲线或测试波形的调制,只需导入PowerArtist产生长时间功耗扫描曲线,该曲线包含了芯片操作的中低频信息,即可结合芯片高频工作模式下的芯片电源模型CPM来进行调制拓展出全频段的CPM模型。调制完成后的CPM,可以结合在CMA里导入的SIwave抽取的封装或系统电源分配网络模型进行频域阻抗扫描以及时域瞬态分析。

图11 CPM调制及芯片-封装-系统仿真流程

CPS 热分析流程

堆叠方式提高了芯片的集成度,但功率密度的提升也给散热设计带来了很大的挑战,2.5D TSV 封装的性能和可靠性受互连焊接点的结构性能影响较大[12],尤其是热应力导致的翘曲等问题,所以散热仿真的精度至关重要。图13展示了CPS 热分析流程图,在此流程中,设计者需要输入EDA设计文件,电磁仿真得到的损耗及芯片的CTM模型,通过Icepak仿真得到芯片及系统的温度分布云图,同时其还将Icepak仿真得到的系统温度分布回推至Redhawk等芯片工具中进行Thermal aware EM signoff。

图13 Ansys CPS Thermal 仿真流程

而对于Interposer等结构的热分析,Ansys提供了全新的RedHawkSC-ET仿真平台,通过3DIC模板,在该平台可以直接导入3DIC各芯片的CTM,并结合封装设计和PCB系统设计,进行CPS热仿真得到芯片及Interposer的热分布以及散热能力,进而评估芯片的可靠性。在此分析过程,CTM模型的引入极大地提高了热仿真的精度,传统方式用户普遍使用Power Map描述芯片工作时的功耗分布,但实际上,芯片的漏电流功耗会随着温度变化而变化,但Power Map无法表征,RedHawk在抽取CTM时,可以包含以下特性,进一步提高热仿真的精度。

器件自发热

温变的漏电流功耗

金属分布密度

散热仿真的另一个挑战来自于电热协同仿真,由于2.5D/3D芯片电源网络的工作电流较大,电流流经电源平面后产生的焦耳热将会抬高芯片周围的温度,而温度变化则会影响通道材料的电导率变化,从而影响其传输性能。通过SIwave-DC与Icepak协同将可准确模拟这一过程,其中SIwave-DC会首先计算电源通道的DC损耗做为Icepak热仿真的输入,而Icepak通过热仿真得到温度后,可将结果传递给SIwave-DC重新计算DC损耗,通过多次仿真迭代达到稳态后,可得到精确的温度分布和DC损耗。

4

结论

2.5D/3D芯片的蓬勃发展,相当于让芯片在高度方向上有了一个扩展,把平房变成高楼,就可以在芯片面积不变的情况下塞下更多器件,同时大幅提高信号的接口性能、降低芯片功耗等。EDA仿真工具的不断发展,通过基于芯片模型的CPS协同多物理场耦合仿真技术,能够让设计者更加高效的应对这些挑战,也是目前主流的仿真手段,在本文介绍的流程中,通过CPM/CSM/CTM等芯片模型的使用,可以在系统仿真时更加准确的获取芯片的特性,使得芯片设计与封装/PCB设计更加紧密的结合在一起,进行协同仿真验证,同时基于电、热的双向耦合等方法,也大大提高了系统仿真的精度。

但从发展趋势看,各EDA厂家的发展思路和方向仍有一些区别,在电磁仿真方向上,有的工具引入更多的模型自动简化功能降低仿真计算量,有的工具通过快速算法提高仿真效率,但以上两种方式都只适合于特定的模型及结构,对仿真精度要求较高的场景还是需要随着计算机高性能计算技术的发展,不断提高3D仿真器的效率,能够实现全波3D仿真工具对Interposer/TSV等结构精细建模;在多物理场耦合仿真的方向上,电热耦合/热应力的耦合场景也会越来越多,传统的仿真工具受限于计算机资源的限制,无法处理全芯片/Interposer模型,通过等效的模型描述芯片的热特性,进行芯片/系统的热环境信息交换,可有效提高仿真效率,也是目前主流的工具展方向, EDA工具在未来也会不断提升芯片模型的信息及精度,进一步提高热/结构的仿真精度。

参考文献

[1] 张江涛,余斌,庞健,等. 2.5D芯片高速接口的SI&PI分析方案[C]//Ansys中国2020用户大会论文集.2020:3-7

[2] 浅谈先进封装技术 [EB/OL]. [2020-10-11]. https://moore.live/news/245867/detail/

[3] Liu L P,Zhang S Q, Luo S, 2.5DIC HBM Chip-Package-System (CPS) Signal Integrity Simulation[C]//Ansys中国2020用户大会论文集.2020:7-8

[4] Joohee Kim, High-Frequency Scalable Modeling and Analysis of a Differential Signal Through-Silicon Via[J], IEEE TRANSACTIONS ON COMPONENTS PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 4, APRIL 2014:1-2

[5] Jun S P, KIM J, CHO J,2-PDN Impedance Modeling and Analysis of 3D TSV IC by Using Proposed P-G TSV Array Model Based on Separated P-G TSV and Chip-PDN Models[J], IEEE TRANSACTIONS ON COMPONENTS PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 1, FEBRUARY 2011:10-11

[6] KIM J, Jun S P, CHO J,High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV) [J], IEEE TRANSACTIONS ON COMPONENTS PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 1, FEBRUARY 2011 :12-13

[7] Jun S P,Slow Wave and Dielectric Quasi-TEM Modes of Metal-Insulator-Semiconductor (MIS) Structure Through Silicon Via (TSV) in Signal Propagation and Power Delivery in 3D Chip Package[C]// 2010 Electronic Components and Technology Conference:1

[8] COGONI D, Put a Cap on DDR System Power Supply Noise[J], Ansys ADVANTAGE ISSUE 3 | 2018:44-45

[9]CoWoSL,TSMC[EB/OL],[2021], https://3dfabric.tsmc.com/schinese/dedicatedFoundry/technology/cowos.htm

[10] LIANG L,3D Modeling and Electrical Characteristics of Through-Silicon-Via (TSV)in 3D Integrated Circuits[C]// 2011 International Conference on Electronic Packaging Technology & High DensityPackaging,2011:1-2

[11] MCMORROW S,Deep Channel Analysis for High-Speed Interconnect Solutions [J], Ansys ADVANTAGE ISSUE 3 | 2017:1-2

[12] LU Y, A New 2.5D TSV Package Assembly Approach[C], //2013 Electronic Components & Technology Conference,2013:5

[13] SONG T, LIM S K, A Fine-Grained Co-Simulation Methodology for IR-drop_SIwave[C]//2011 IEEE 20th Conference on Electrical Performance of Electronic Packaging and Systems,2011:2-4

[14] SCHREURS P,Fatigue damage in solder joints[C]//Fifth World Congress on Computational Mechanics July 7–12, 2002, Vienna:1

[15] ZAHN B A, Finite Element Based Solder Joint Fatigue Life Predictions for a Same Die Stacked Chip Scale Ball Grid Array Package[C]// 27th Annual IEEE/SEMI International Electronics Manufacturing Technology Symposium:1-2

[16] GAIKWAD N V, RELIABILITY OF A 2.5D TSV PACKAGE[D], ARLINGTON, THE UNIVERSITY OF TEXAS AT ARLINGTON,May 2018:4-6

[17]3DFabric's Complete System Integration Portfolio,TSMC[EB/OL],[2021], https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/3DFabric.htm

“微系统与先进封装技术”专题(电子版)可点击下方查看

点击查看完整内容

关于作者

褚正浩 | Ansys高科技行业专家

研究方向为芯片、封装及系统协同仿真技术。于2012年加入Ansys,有多年的高速信号及电源完整性设计经验,目前主要负责Ansys中国High-tech行业的技术方案规划,为Ansys的客户提供信号完整性、电源完整性、电磁兼容方面的技术支持。在加入Ansys之前,曾在Cadence-Sigrity公司以技术支持工程师的身份负责北方区客户的信号完整性、电源完整性的技术支持。

张书强 | Ansys 半导体事业部技术经理

一直从事芯片-封装-系统协同设计和协同仿真领域的技术支持工作,主要研究领域:芯片-封装-系统电源/信号/热完整性协同仿真分析,芯片功耗噪声签核分析。

侯明刚 | Ansys 主任工程师

哈尔滨工业大学自控专业,在控制系统、高速互连和电磁干扰领域拥有十多年从业经验,拥有大量使用仿真软件解决工程设计问题的实战经验,负责芯片-封装/电路板-系统(CPS)协同仿真设计解决方案,通过芯片到系统的电、热、力多物理耦合分析,全面提升电子产品设计可靠性。

想要了解更多Ansys CPS解决方案,可查看近期『2021 Ansys Innovation大会』——CPS-芯片封装系统专题分会场,>>成为Ansys数字资源中心会员查看更多精彩内容