HFSS中的TDR仿真那些事-从高速过孔位列说起

本文摘要(由AI生成):

文章主要讨论了HFSS信号完整性仿真中TDR仿真的相关问题。作者指出,很多人对软件的细节了解不够深入,导致仿真结果存在问题。HFSS提供了两种观察TDR的方法,一种是使用HFSS transient,另一种是使用driven terminal+插值法宽频扫描。作者建议在仿真前了解TDR测试原理,有助于理解仿真结果。在HFSS中,扫频范围会影响TDR,因为扫频范围必须包含足够多的频谱分量,才能形成想要的rise time。作者提供了计算截止频率fmax的公式,并介绍了验证手段。此外,作者还讨论了模型问题,指出当模型很小且使用wave port时,不能直接看TDR,最好使用deembedding。

近期看了一些HFSS信号完整性仿真的文章,发现很多人对软件的细节了解不够深入,要么使用各种小工具,要么仿真出来的曲线一看就是存在问题的。对于辅助小工具,如果对软件使用还不够纯属的时候,我是比较反对的,如果你对软件各方面都很了解,那么就无所谓了;至于仿真结果不对,还是help文件看的少,软件的用法不对,尽管你觉得是对的。

TDR仿真是高速应用经常要观察的一个指标,HFSS提供了两种观察TDR的方法,一种方法是使用HFSS transient,纯正的时域仿真求解器,不过我看很多人几乎没用过该功能,其实transient在layout前仿真还是很有用的,求解速度挺快,看TDR也很方便;另外一种就是大家常用的driven terminal+插值法宽频扫描,但是这是纯粹的频率求解,而TDR又是时域的结果,所以软件提供了IFFT这种算法,将频率求解得到的S参数转换为时域的TDR。

既然是从频域转换到时域,要么问题来了!!假如我仿真的信号速率是10Gbps,对应的每bit时间为100ps,那么信号的rise time大概为35ps,要形成一个rise time为35ps的step信号,在HFSS中扫频的范围该怎么设置?设置为多大才比较合适?很多人的问题就出现在这里。 这里建议大家去了解下TDR的测试原理,有助于你理解仿真的结果。

为什么扫频范围会影响TDR呢,这跟时间分辨率也就是信号的rise time有关,rise time越小,信号包含的高频分量就多,因此在HFSS设置的扫频范围必须包含足够多的频谱分量,才能形成我们想要的rise time,在HFSS中,rise time=1/fmax,fmax为扫频的最大值,即截止频率,你可以通过这个公式来计算你的截止频率。

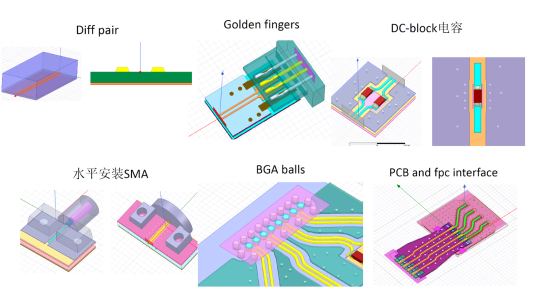

上述公式正确与否,在ANSYS electronics desktop里面有好几个验证手段,简单的就是在电路仿真circuit simulator里面分析不同rise time step信号的频谱,取一阶包络对应的频率分量,如下图:非常简单的一个电路模型,然后分析电压V1在不同上升沿时间下的频率。可以看到,当tr分别取100ps、35ps、15ps,仿真的最大频率fmax分别为9.89GHz、28.67GHz、66.63GHz,你可以通过上面的公式分别计算以下,两者的结果是很接近的。

另外一个手段就是借助于HFSS transient,根据这里面频谱的对应关系,来确定fmax的值,参考下面三图,直接mark处fmax即可,可以看到跟电路仿真的值也很接近。

上面说了要得到正确的rise time,应该怎么样计算fmax以及其验证手段,下面我们看过孔TDR分析的例子。

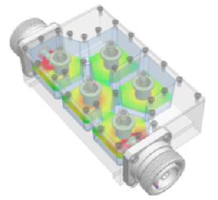

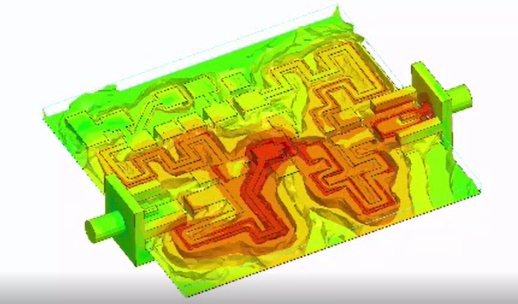

我是在HFSS 3d layout中建立的模型,其求解算法跟HFSS是一样的,因此不影响我们的结果分析。模型图片如下:典型的过孔模型,差分阻抗为82.53ohm,过孔阻抗未知。

当求解截止频率分别设置为10GHz、30GHz、75GHz是,对应的rise time大概为100ps、35ps、15ps,我们对比过孔在不同rise time的阻抗表现,因为模型很小,我们应用了wave port的deembedding,非常有用的一个技能。

从下图可以看到,当rise time=100ps时,整个通道阻抗差分阻抗差不多就是100ohm,过孔和差分线都表现为理想的传输线,寄生效应不明显;当rise time=35ps时,差分线仿真阻抗为82.06ohm,非常接近于polar si9000的计算值,这样证明了仿真各方面的设置是正确的,此时过孔的阻抗为97ohm;当rise time=15ps时,过孔阻抗为112ohm,这就说明在不同的rise time下,同样的结构,其阻抗特性截然不同,因此fmax的选择,将极大的影响你的仿真结果。

有人可能会想,我直接在HFSS TDR options窗口中更改rise time行不行呢?答案是不行的,如下两图:显然直接更改rise time和跟正确设置rise time得到的TDR相比,还是有很大差异的。

上面的仿真数据对比说明,一定要根据你分析信号的rise time选择合适的fmax,不然仿真出来的结果跟实际的会有很大出入,同时你基于此仿真结果优化结果也是无意义的,谨记。

这里再说一下模型的问题,因为当前模型中过孔的model很小,使用的又是wave port,已经犯了wave port设置的大忌讳,即wave port距离阻抗不连续结构不能太近,这会导致S参数计算精度不够,详细可以参考help文件。因此,你要么加长差分线的长度,要么使用wave port的deembedding功能来变相加长差分线,让wave port距离过孔有足够远的距离,不然的话直接看TDR是非常不准的,结果如下,不做deembedding看的TDR非常好,事实上差分线阻抗只有82.6ohm,完全不对,同时TDR曲线持续的时间很短,你也没法区分到底哪个时间点对应的TDR才是过孔的阻抗,做了deembedding就很好区分,肯定中间突起的就是过孔阻抗。

以上就是这次分享的HFSS中TDR仿真要注意的事项:

要根据你产品的速率,来选择合适的fmax;

模型很小时,又使用wave port时,不能直接看TDR,最好使用deembedding;