反相输入比例运算电路如下图所示,

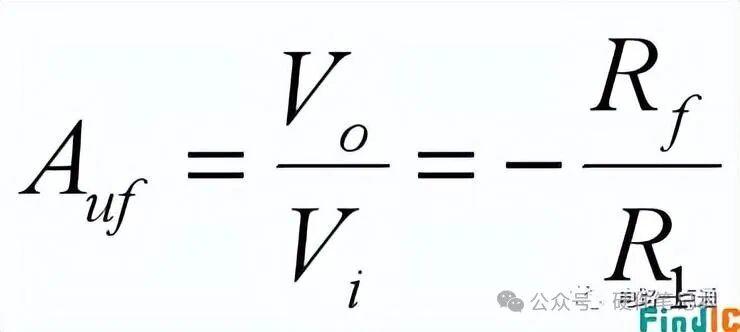

其电压放大倍数为

在实际应用时应注意:

(1)此类电路的电压放大倍数不宜过大。通常Rf宜小于1MΩ,因Rf过大会影响阻值的精度;R1不宜过小,R1过小将要从信号源或前级吸取较大的电流。

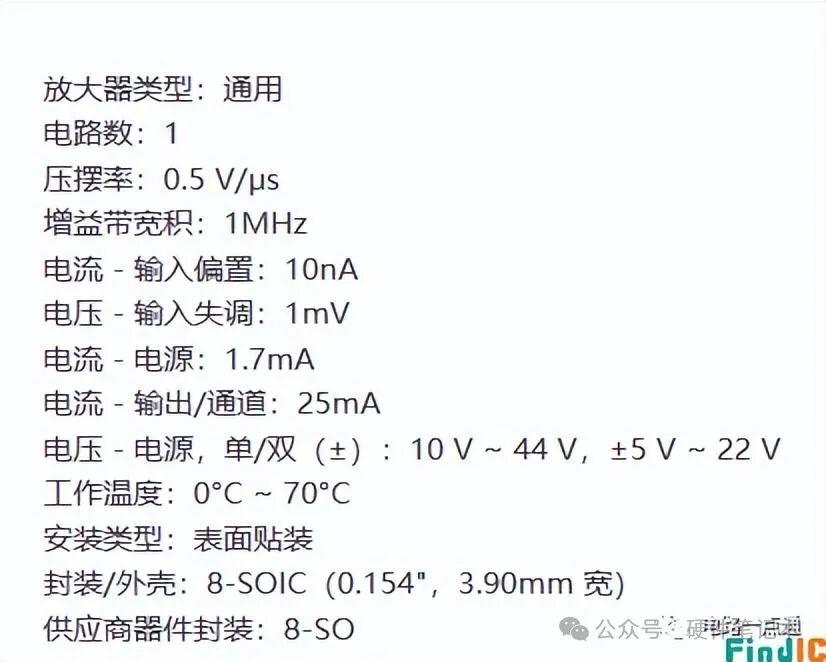

(2)作为闭环负反馈工作的放大器,其小信号上限工作频率fH 受运放增益带宽积GBW= Avd*fH的限制。以μA741为例,μA741基本参数如下:

其开环差模电压放大倍数Aud=10^5倍,开环fH=10Hz,故运放的单位增益上限频率fT=1MHz,即作为电压跟随器或反相器工作时的最高工作频率为1MHz。若用μA741设计Auf为20dB即便10倍的放大电路,则电路允许的上限频率为100kHz。

(3)如果运放工作于大信号输入状态,则此时电路的最大不失真输入幅度Vim及信号频率将受运放转换速率SR的制约。仍以μA741为例,其SR=0.5 V/μs,若输入信号的最高频率为100kHz,则其不失真最大输入电压Vim<=(SR)/(2*pi*fmax)=0.5*10^6/2*pi*10^5=0.8V。

SR:压摆率单位时间(一般用微秒)器件输出电压值的可改变的范围。

(4) 该电路中R1=RF时 ,Au=-1,Uo=-Ui,为反相器。

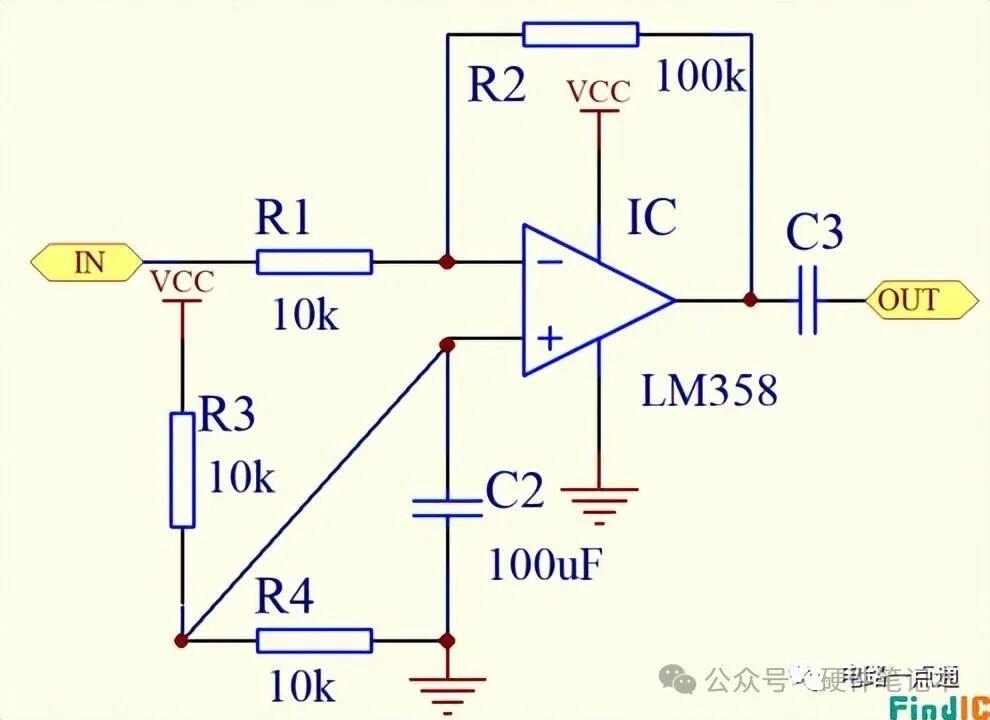

2、单电源供电反相交流放大器

单电源供电反相交流放大电路以LM358为例,电路图如下所示:

该反向放大器的特点和使用技巧:

(1)输出信号与输入信号反相。

(2)输入阻抗较低,约为R1,这是我们不希望的。

(3)输出阻抗较小,这一指标较好。

(4)电压放大倍数由R1和Rf比例确定,可以做的比较高。

(5)共模抑制比CMRR较好。

推荐电压放大倍数不大于30dB(约33倍),R1和Rf可在1千欧~几百千欧间选。一般R1取值范围1k~20k,Rf取值为(1~33)R1。这里指出一个误区,在电子设计制作或实验时,往往加大Rf/R1的值,以获得大的Au,以为Au越大越好,事实上,当Au>33时已超出运放的线性范围,是不可取的,应予注意。

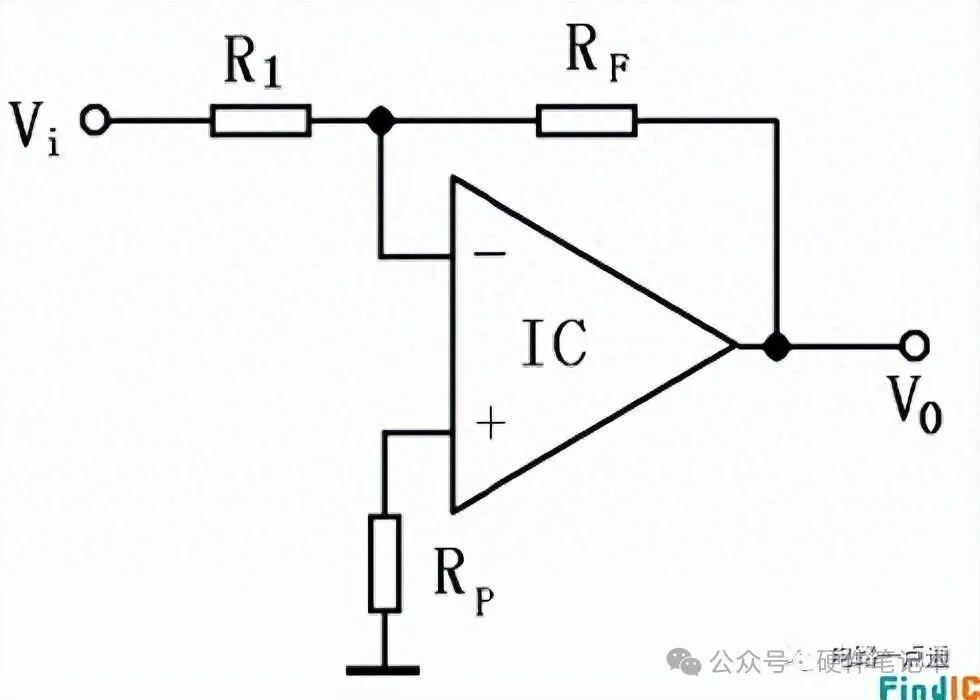

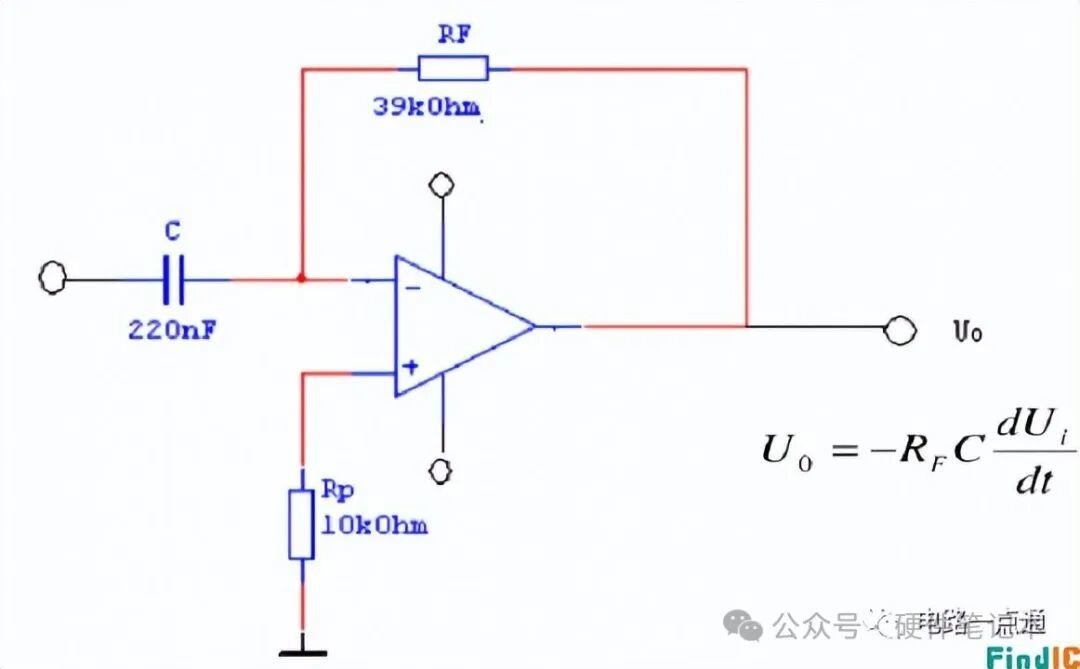

3、同相输入比例运算电路

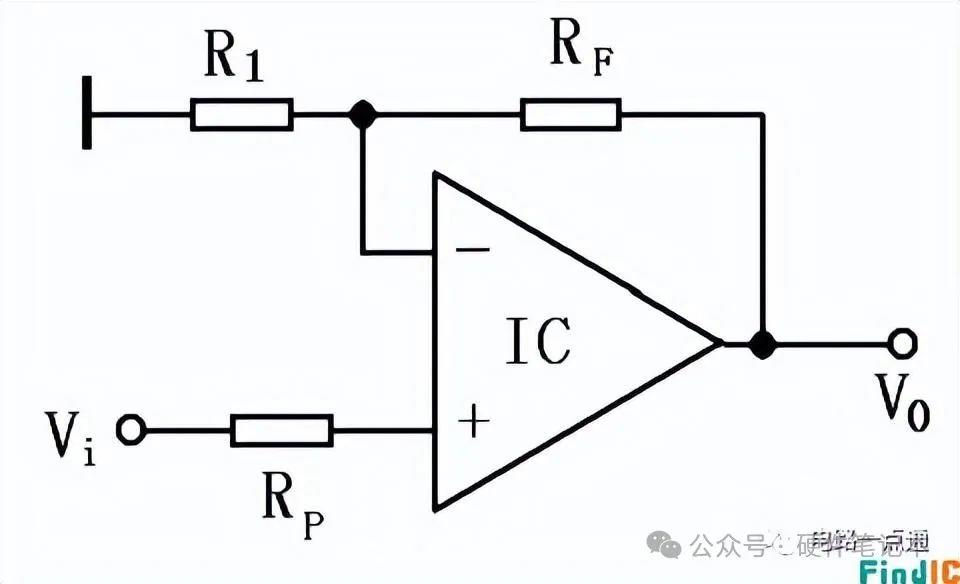

同相输入比例运算电路如下图所示,

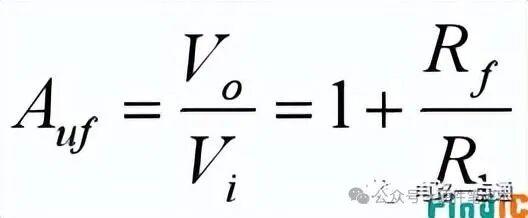

其电压放大倍数为:

为使输入电流引起的误差最小,应取平衡电阻Rp=Rf//R1。当Rf//R1=0时,即使用一根导线替代Rf,Auf=1,电路演变成为电压跟随器。

该同向放大器的特点和使用技巧:

(1)输出信号与输入信号同相。

(2)电压放大倍数由R1与RF的比例确定,可以做得比较高。

(3)由于电路引入深度电压串联负反馈,使得输入电阻增加(1+AF)倍,可高达几兆欧,输出电阻减少1/(1+AF倍),一般可视为0.。

(4)同向放大器的共模输入电压不为0,所以共模抑制比CMRR较小。

使用时推荐电压放大倍数不大于30dB(约33倍),R1和Rf可在1千欧~几百千欧间选。一般R1取值范围1k~20k,Rf取值为(1~33)R1。Au,R1,RF的选取和反向放大器一样。

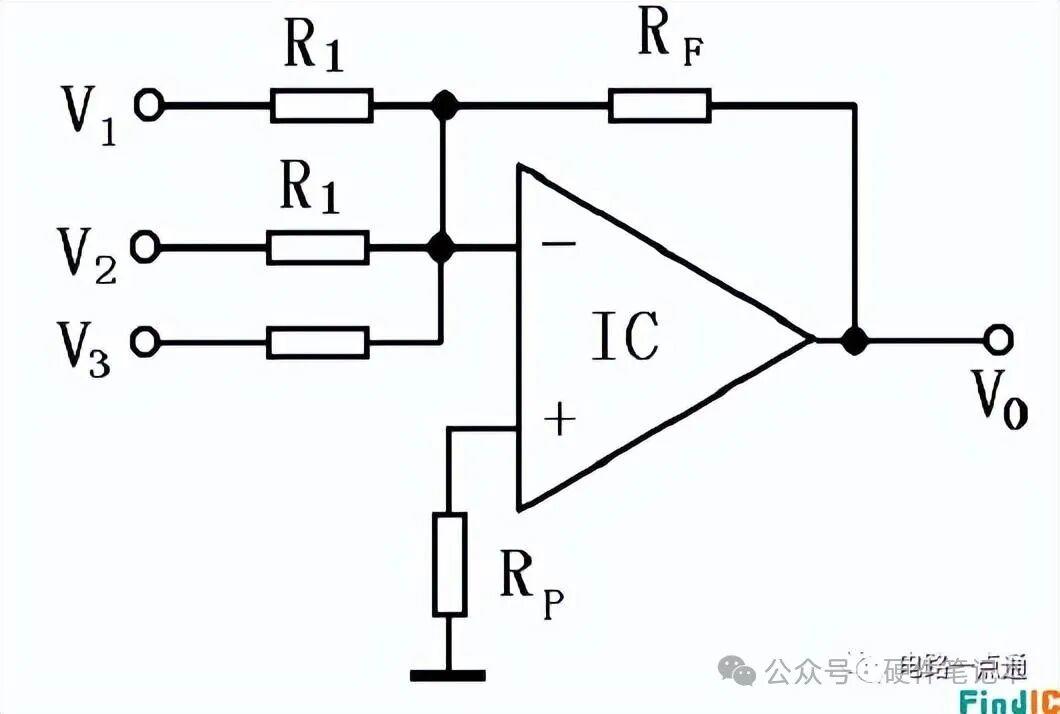

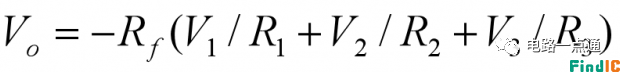

4、反相输入比例求和电路

反相输入比例求和电路如图所示,

其输出电压为

平衡电阻Rp= Rf// R1// R2// R3。

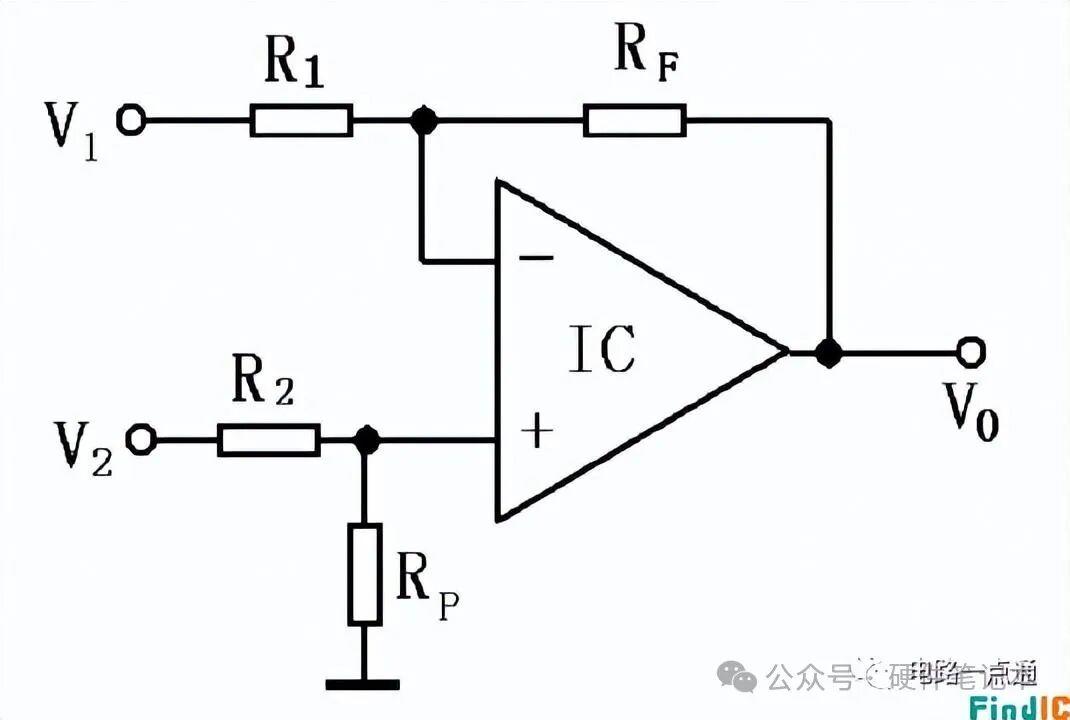

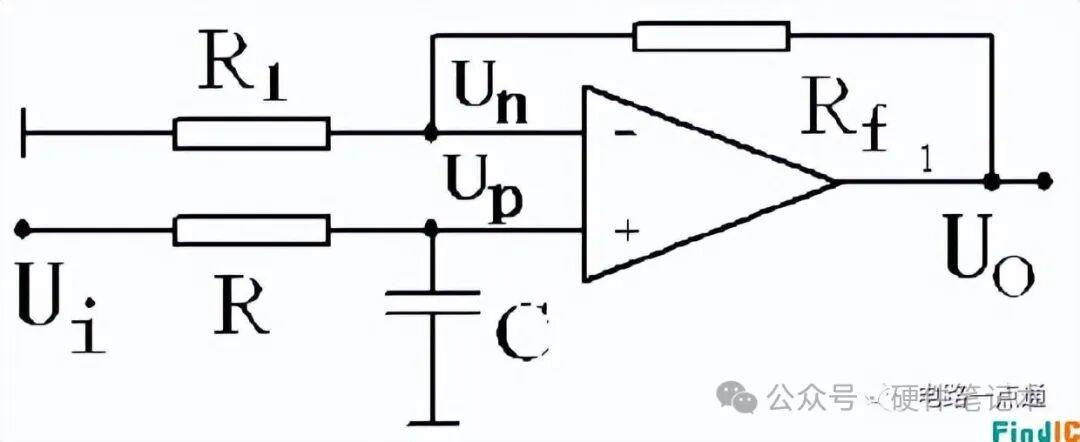

5、差动放大电路

差动放大电路如图所示,

其输出电压为Vo= -(Rf/ R1)*V1+(1+ Rf/ R1)*(1+ R3/ (R2+ R3))*V2

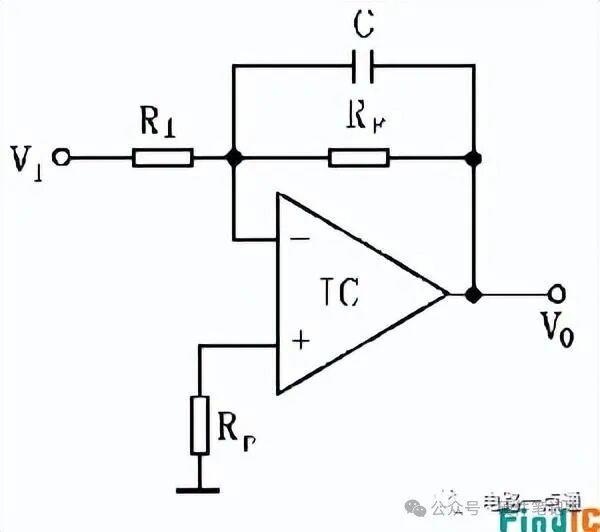

6、积分运算电路

积分运算电路如图所示。

其输出电压为

电路中电容为反馈电容。可以实现波形变换,将矩形波变为锯齿波,还可实现移相90°、延时等。通常,为限制低频电压增益,在积分电容C两端并联一个阻值较大的电阻Rf。当输入信号的频率:fi>1/(2*pi* RfC)时,电路为积分器;若fi<<1/(2?*pi*RfC),则电路近似于反相比例运算器,其低频电压放大倍数Avf约等于-Rf/ R1 。当Rf=100kΩ、C=0.022uF时,积分与比例运算的分界频率约为1/(2*pi*pi*RfC)= 1/(2*pi*100*10^3*0.022*10^6)=72Hz。

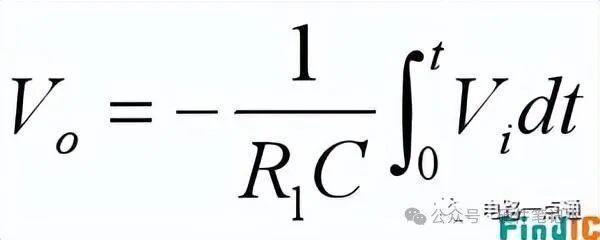

7、微分电路

将积分电路RC互换位置,便得到微分电路。能将矩形波变为正负尖脉冲,能将输出信号超前移相90度。电路图如下所示:

8、信号滤波器电路

按频率特性分,滤波器分低通、高通、带通、带阻、全通。LC滤波器一般用于高频电路,RC滤波器一般用于低频电路。例:一阶低通有源滤波器如下图所示。

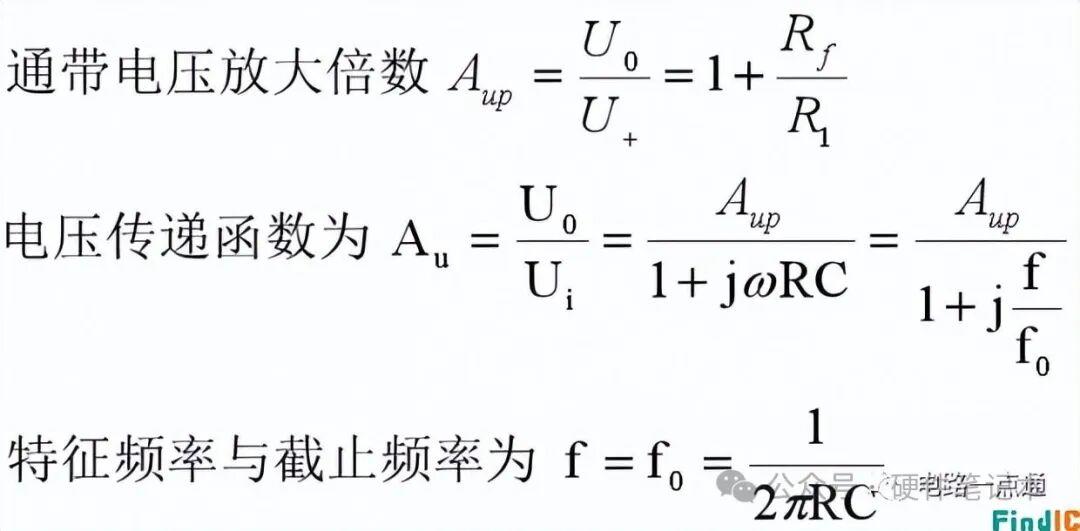

电路中参数计算如下: