直流无刷电机驱动电路

前言

前言

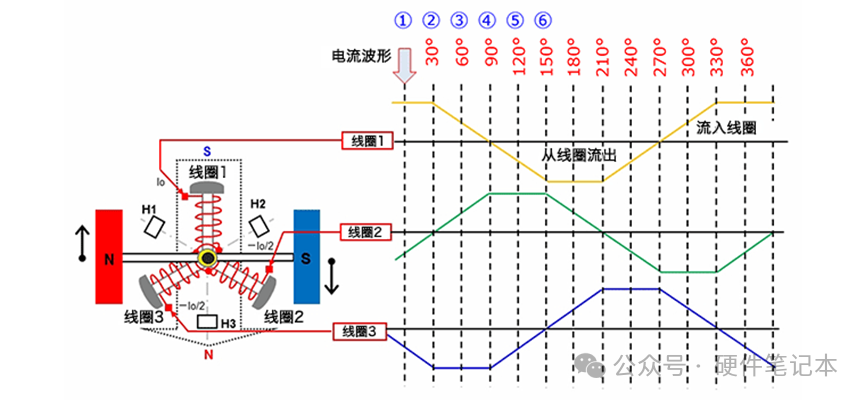

由于无刷电机具有高扭矩、长寿命、低噪声等优点,已经在各领域中得到了广泛应用。其内部电子绕组可看作一个电感线圈。如图1所示内部结构及电流波形,通过不断改变定子绕组中的电流方向,从而改变电磁铁的磁性,使得电机连续旋转。因此需要设计一个驱动电路,改变定子绕组中的电流方向才能使得转子旋转,常用驱动电路为三相全桥逆变电路。

图1 电机内部定子绕组结构及电流波形

三相全桥逆变电路

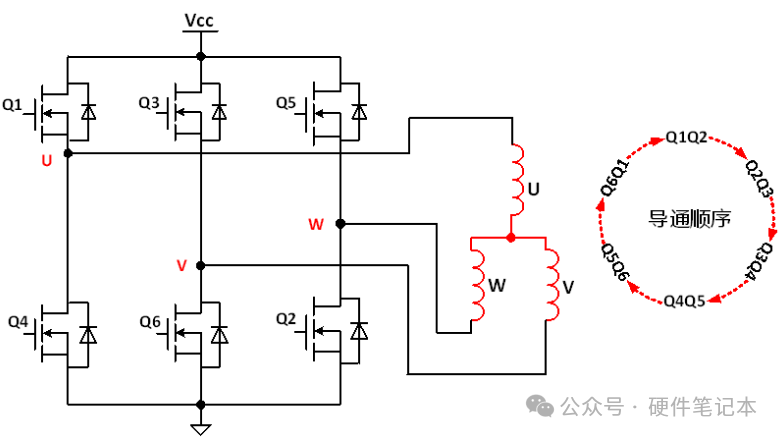

无刷电机驱动三相全桥逆变电路以及工作时序如图2所示,无刷电机中有3个绕组,分别为U、V、W相绕组。每个绕组中电流有2个方向,所以三相电机中电流的方向有3*2=6个,通过控制三相桥电路中3个绕组中的电流方向,使其按照一定的规律改变方向,来实现三相电机的连续运转。通过控制PWM信号的不同占空比,实现输出电压的变化来控制电机的转速。

图2 三相全桥逆变电路及工作时序

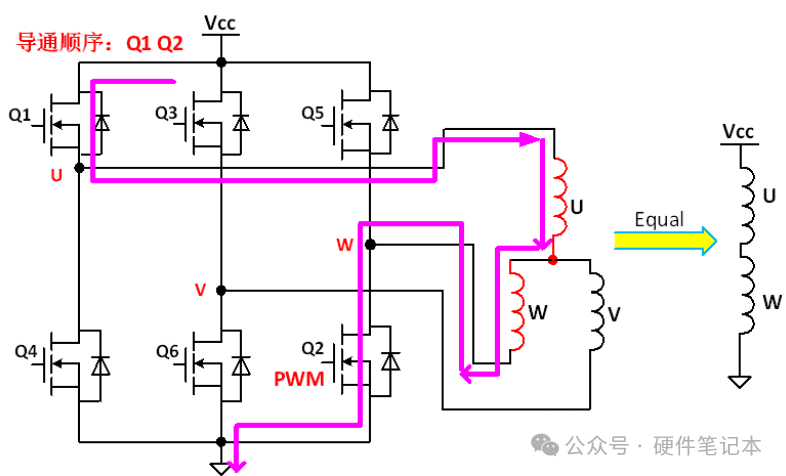

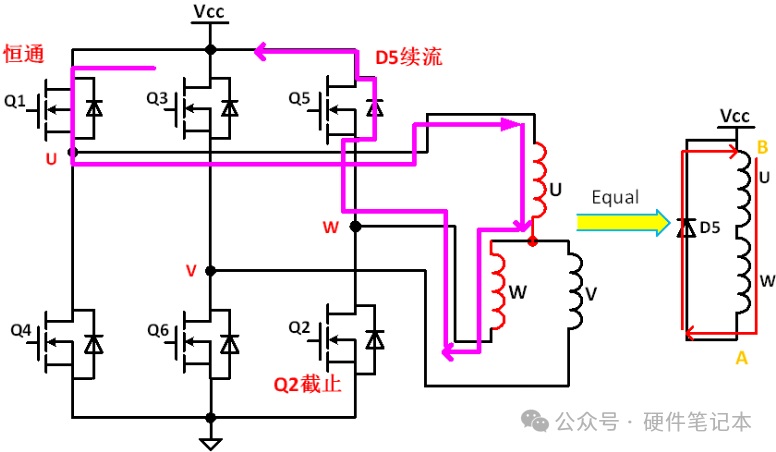

如图3所示,在Q1、Q2导通时序内, Q1保持恒通,Q2使用PWM斩波(也可以让Q2保持恒通,Q1使用PWM斩波,但该方式高边PWM驱动较难实现),如PWM的占空比为50%,则加在电机绕组两端的平均电压就是Vcc*50%。

图3 Q1 Q2导通时序电路流

当Q1导通,Q2截止的时候,由于绕组电感特性,电流要保持方向和大小不变,此时绕组相当于电流源,电流从源的正端W端出发,经过Q5体二极管D5续流,回到源的负端U端,如图4所示。AB两点间的电压被D5钳位在0.7V。此时MOS管的功耗称为续流损耗,续流损耗计算式为P=0.7V*Id。

图4 Q1 Q2导通时序电路流

热损耗分析

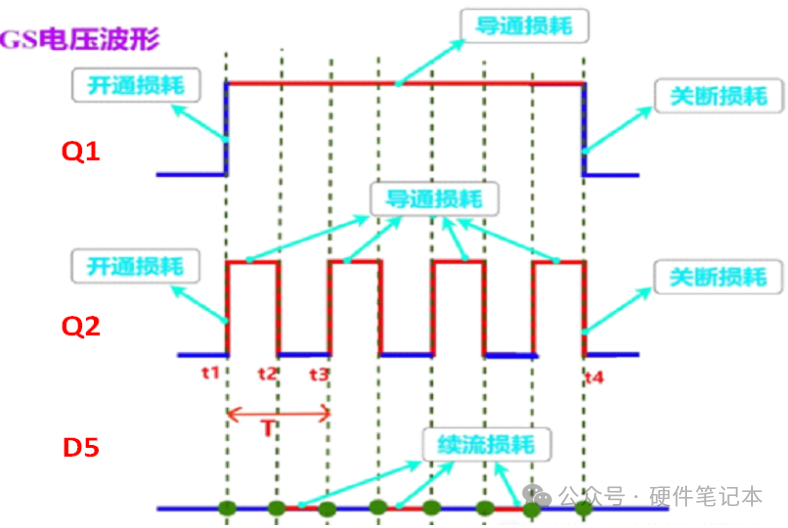

以第一步导通相序Q1 Q2为例,总时间从t1到t4这段时间(单个时序工作60°),如图5所示。t1到t4时间内,Q1只有导通损耗(忽略一次开通损耗和一次关断损耗) ,Q2有开关断损耗、导通损耗。Q5寄生二极管D5有续流损耗。

图5 第一步导通时序损耗组成

以某电动自行车为例,Vcc供电电压48V, 回路中的电流Id是10A,占空比为50%,开关频率为20kHz。假设MOS管的导通电阻Rdson=10mΩ,t1到t4相序内,Q1只有导通损耗:

Q2的损耗包括开通损耗、导通损耗、关断损耗,先看一个PWM周期内的损耗,当PWM为高电平时,Q1和Q2同时导通,假设PWM的占空比是50%, PWM的周期为T, 那么在t1到t2时间段内,Q2的导通损耗:

假设 100ns ,Q2的开关损耗:

100ns ,Q2的开关损耗:

二极管的压降0.7V,D5的续流损耗:

在第一步导通相序内,续流损耗大于开关损耗, Q5最热,Q2次之,Q1温度最低。如在其他小功率应用中,回路中的电流流过1A时,则寄生二极管续流损耗0.35W,Q2最热,D5次之,Q1温度最低。

基于以上小功率与中等功率对比,存在一个规律:小电流时,谁斩波谁热;大电流时,谁续流谁热。

续流方式对比

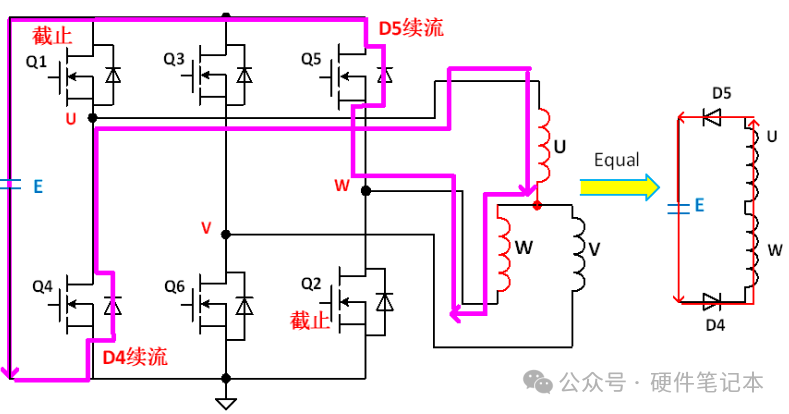

在t2到t3时间段内,Q1导通,Q2关断,Q5关断。此时电流从Q5的体二极管流过,电感两端的电压被钳位在0.7V,所以,0.7V=L*di/dt,di/dt=0.7V/L。此时di/dt很小,也就是电流的变化速度很小。这说明在t2到t3时间段内,电感的续流电流下降很缓慢,称为慢续流,也叫高端续流。对于电机来说,电机绕组上有电流,电机才能输出力矩,因为慢续流时Id电流下降的速度很慢,所以电流下降到0的时间也很长,这就保证了在续流期间,电机绕组上仍然是有电流的,也就是电机在续流期间仍然可以输出力矩。但是,有的时候并不希望电机绕组在续流器件仍然有很大的电流,如主流新能源汽车都带有能量回收功能,也就是在刹车的时候,需要电机绕组上的电流在很短的时间内降为0,这个时候就需要快续流了,让电流的变化速度快,电流能够在短时间内变成0,能量回馈至输入电源端。

电感续流如图6所示,将Q1与Q2都截止,此时电流会通过Q5和Q4的体二极管续流,并且电流是通过输入电源形成回路的,此时对输入电源进行充电,因为W端出来,经过Q5的体二极管D5,有一个0.7V的压降,然后连接输入电源,所以W端是E+0.7V。GND经过的Q4的体二极管D4有一个0.7V的压降,之后连接到了电感的负端(U端),那电感的U端就是-0.7V,电感的感应电动势E+0.7V。根据公式:U/L=di/dt,慢续流时0.7V,快续流时E+0.7V。di/dt的结果比慢续流时大很多,此时电流变化的速度很快。

图6 快续流电路图

声明:

声明:文章整理于网络。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。

声明: