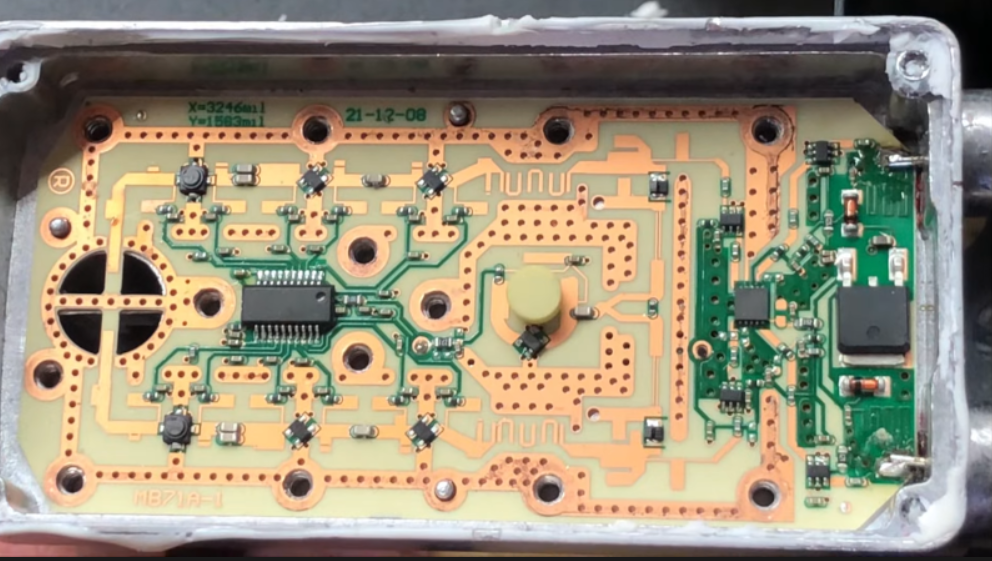

一款20 GHz LNB(低噪声降频器) 电路板

上图是一个工作在20GHz 的低噪声降频器LNB,集成了信号极化处理、射频放大、滤波器、高侧本振、混频器及支持电路等一系列复杂功能模块。

信号极化处理是 LNB 的关键功能之一。不同极化方式的信号在传输过程中具有独特特性,LNB 需要精准识别和处理水平极化、垂直极化、左旋圆极化或右旋圆极化信号,确保信号的正确接收与传输。这一功能要求 RF PCB 设计必须考虑极化信号的隔离与传输优化,避免不同极化信号间的相互干扰,保证信号的完整性。例如,在设计用于卫星通信的 LNB 时,需要在 PCB 上合理规划不同极化信号的走线,采用屏蔽措施防止串扰。

射频放大模块负责对微弱的射频信号进行增强,以便后续处理。在这个过程中,不仅要保证信号的放大增益,还要严格控制噪声系数,降低噪声对信号质量的影响。对于 RF PCB 设计而言,这意味着要精心选择合适的放大器件,并优化其在 PCB 上的布局与布线。比如,将低噪声放大器(LNA)尽可能靠近信号输入端,减少信号在传输过程中的损耗和噪声引入;同时,合理规划电源和接地路径,为放大器件提供稳定的工作环境,降低电源噪声对放大信号的干扰。

滤波器在 LNB 中用于筛选出所需频段的信号,抑制无用频段的干扰信号。不同类型的滤波器,如低通滤波器、高通滤波器、带通滤波器等,在 LNB 中发挥着各自的作用。RF PCB 设计需要充分考虑滤波器的特性,确保其与其他电路模块的良好匹配。例如,在设计带通滤波器时,要精确计算和调整滤波器的参数,使其中心频率和带宽满足 LNB 的工作要求;并且在 PCB 布局上,将滤波器与其他敏感电路保持适当距离,避免相互干扰。

高侧本振为混频器提供所需的本振信号,其频率稳定性和相位噪声对 LNB 的性能至关重要。在 RF PCB 设计中,需要为高侧本振电路设计独立的电源和接地平面,减少电源波动和地噪声对本振信号的影响;同时,采用合理的屏蔽和滤波措施,抑制本振信号的泄漏,防止其干扰其他电路模块。

混频器作为 LNB 的核心模块之一,将输入的射频信号与本振信号进行混频,实现信号的频率转换。这一过程对 RF PCB 设计提出了严格的要求,包括信号的隔离、阻抗匹配以及杂散抑制等。比如,在 PCB 布局上,要将混频器的输入、输出端口进行有效的隔离,防止信号反射和串扰;并且要精确控制混频器的阻抗匹配,确保信号在混频过程中的高效传输,减少信号损失和失真。

此外,LNB 中的支持电路,如偏置电路、控制电路等,虽然看似辅助功能,但同样不可或缺。这些电路的设计和布局也会影响 LNB 的整体性能。例如,偏置电路需要为各个有源器件提供稳定的偏置电压,其设计不当可能导致器件工作不稳定;控制电路用于实现 LNB 的各种功能控制,如增益调节、频段切换等,其信号的传输和处理需要在 RF PCB 上进行合理规划,避免与其他信号产生干扰。

注释:射频学堂原创或者转载的内容,其版权皆归原作者所有,其观点仅代表作者个人,射频学堂仅用于知识分享。如需转载或者引用,请与原作者联系。