客户之声|InspireSemi 借助 Cadence 数字签核工具为下一代 AI 铺路

InspireSemi 致力于为 HPC、AI、图形分析和其他计算密集型应用开发和提供卓越的加速计算解决方案。InspireSemi 致力于打造开放、多功能的架构,具有极快的速度、节能、开发人员友好的全 CPU 编程模型和改变游戏规则的经济实惠性,因此在与创新者合作方面具有独特的优势。

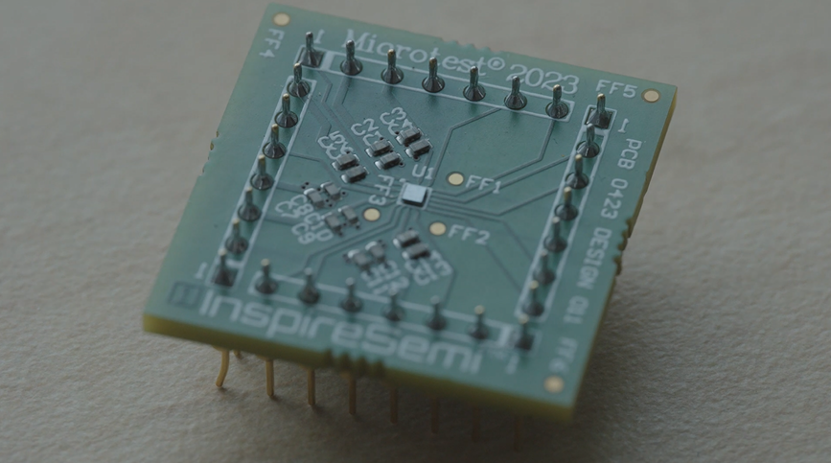

高性能计算 (HPC)、人工智能 (AI) 和图形分析计算解决方案价格昂贵、编程复杂、能耗较大且适用范围有限。InspireSemi 的片上系统 (SoC) Thunderbird 从多个层面颠覆下一代加速计算,包括原始性能、广泛适用性、低能耗和经济性。该系统采用全 CPU 架构,更易于编程,并且适用于所有高性能计算和 AI 应用。借助 Cadence 的 Digital Full Flow 与 Innovus Implementation System、Genus Synthesis Solution 和 Tempus Timing Solution,Thunderbird SoC 成功完成了流片。

“客户告诉我们,现有的 HPC-AI,和图形分析计算解决方案还不够好,它们价格昂贵、编程复杂、能耗较大且适用范围有限。

大多数人对 GPU 并不陌生,因为它们在机器学习和生成式 AI 等,AI 应用中扮演着重要角色。然而,对于全球政商学三界,日常使用的重要应用而言,GPU 的用途相对有限。革命性 Thunderbird SoC 将在多个层面上实现突破,包括原始性能、广泛适用性、低能耗和经济性。CPU 架构更易于编程,因此适用于所有 HPC-AI 应用,包括汽车、航空航天、网络安全、气候与天气建模、基因组学和制药行业中的重要仿真和建模应用。

自流片工艺推出以来,我们赢得了全球 HPC-AI 媒体和分析师的高度赞誉。我们很高兴能够与这些行业的众多领军者携手合作开发 Thunderbird,其中包括 Sandia 和 Oak Ridge 等国家实验室,以及得克萨斯大学奥斯汀分校的德克萨斯高级计算中心。此外,我们还与多家世界一流的市场拓展合作伙伴建立了合作关系,包括 Lenovo、Penguin Solutions、Dell OEM 和 Worldwide Technologies。近日,我们还荣获奥斯汀商会颁发的小型企业卓越奖。”

—— Doug Norton

( CMO, InspireSemi )

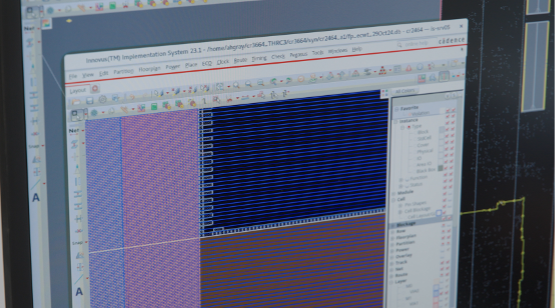

“我们的产品理念围绕优化性能和功率效率,旨在缩短产品上市时间。为了实现性能、功耗和面积目标,我们与 Cadence 保持密切合作。Cadence 在先进节点设计方面处于领导地位且掌握创新签核技术,因此我们决定采用 Cadence Digital Full-Flow,借助 Cadence 的综合数字流程,我们加快了设计融合。所有签核引擎都紧密集成在 Innovus Implementation System 中,帮助我们团队在紧迫的时间内高效完成设计。

我们非常高兴地宣布,借助 Cadence 的 Genus、Innovus、Quantus 和 Tempus 解决方案,成功在 12nm 制程下完成流片。通过使用经 Foundry 认证的 Quantus 进行参数提取以及利用 Tempus 进行静态时序分析和最终签核,我们大大减少了签核收敛迭代次数,由于这些签核引擎与 Innovus 紧密集成,我们可以快速收敛,顺利赶上紧迫的流片截止期限。我们在先前的流片中使用了 Tempus 并获得了良好的结果,我们将继续与 Cadence 合作,以满足当前和未来项目需求。

Cadence Digital Full-Flow 的整体性能和质量,是我们成功按时完成设计的关键。

展望未来,与 Cadence 合作对完成我们的使命至关重要。我们不仅携手打造创新解决方案,还为下一代人工智能和高性能计算奠定了坚实基础。对未来,我们充满期许和信心,相信我们的合作将继续推动这个市场的创新和成功。”

—— Thomas Fedorko

( COO, InspireSemi )