DDR4硬件设计验证和信号完整性仿真精品课40讲—掌握全流程实操 DDR4硬件设计、验证、仿真、测试

- 作者优秀

- 从业经验5+年

- 用户好评

- 课程评分大于4.8,带字好评量大于等于10个

- 内容充实

- 工程案例/内容体系完整

- 平台推荐

- 主编推荐/全网独家

- 增值服务

- Vip答疑服务

服务:

- 课程资料下载

- 90天知识圈

- 在线开票

- 提供培训通知

- 交流群

本课适合哪些人学习:

1、学习型仿真工程师

2、理工科院校学生

3、硬件设计师

4、siwave ads软件学习和应用者

5、DDR测试工程师

6、SI工程师

你会得到什么:

1、掌握DDR4的原理设计、设计注意事项、如何在vivado工程中验证原理设计的正确性

2、掌握DDR4的pcb设计注意事项,阻抗如何控制

3、掌握DDR4的仿真流程:从控制器(ultraScale fpga)到封装 PCB DRAM全流程仿真

4、通过仿真学会如何对DDR4信号质量进行判读

5、完整的工程实例

课程介绍:

DDR4硬件设计 验证 仿真全流程精讲-掌握Siwave、ADS、vivado在DDR4工程中如何使用

课程内容

1 课程介绍

2 硬件设计需求介绍

3 原理图设计指南讲解

4 原理图设计讲解

5 在Vivado软件中对原理设计进行工程验证

6 DDR4 PCB Layout设计指南讲解

7 DDR4层叠阻抗设计

8 PCB设计文件导入Siwave

9 DQ信号及电源的S参数抽取

10 DDR4在ADS中进行写通路仿真

11 DDR4在ADS中进行读通路仿真

12 DDR4地址信号在ADS中仿真

13 抽取DQ及电源S参数注意事项

14 抽取地址信号S参数注意事项

15 VTT电源S参数抽取方式

16 抽取地址信号S参数注意事项

17 VTT信号S参数抽取方式

18 封装RLC参数如何生成及添加进行仿真

19 UltraScale DDR ControllerSettings and IBIS Simulation

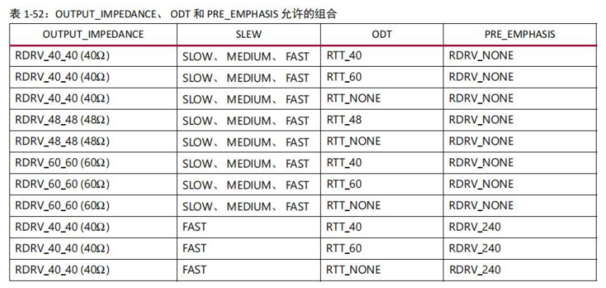

20 DCI控制

21 VREF_CNTR模块

22 Fly_by结构深入研究

23 DDR4写读过程中指标要求

24 IBIS介绍

25 DDR4 interposer埋阻工艺介绍

26 埋阻设计要点

27 9系列FPGA之DDR3原理设计指南

28 9系列FPGA之DDR3 PCB设计指南

29 DDR4仿真总结

课程相关图片: