芯片封装及其热特性分析

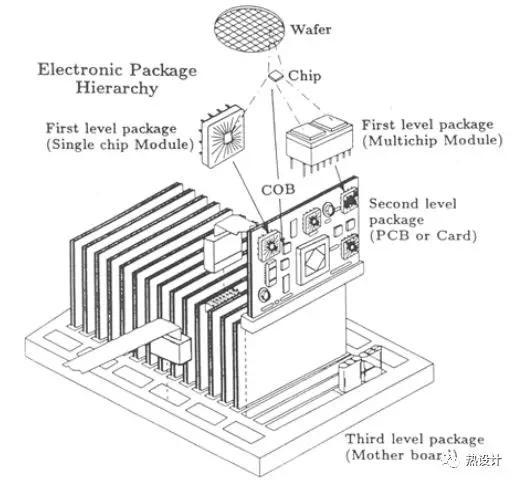

电子产品中,信号的连接有6个等级,分别为:

0级连接:晶圆内部门电路之间的连接;

1级连接:晶圆与封装外围电路之间的连接;

2级连接:元器件与单板之间的连接或元器件与元器件之间的连接;

3级连接:PCB之间的连接,如装有多块单板的背板或主板;

4级连接:子系统之间的连接,如插箱;

5级连接:独立系统之间的连接,如网线连接。

图5-12 各级连接示意图

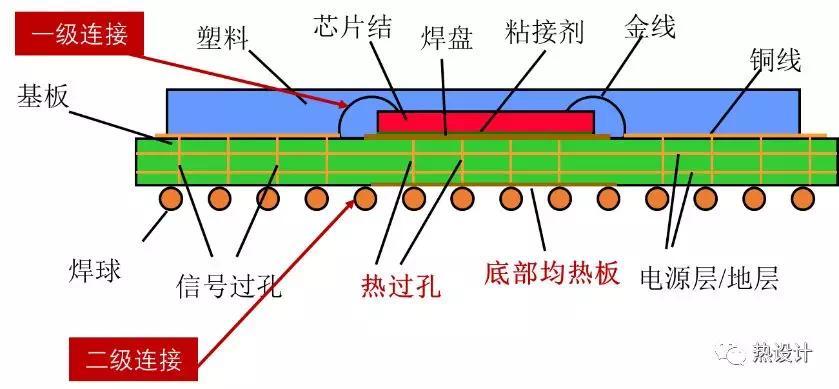

芯片封装热特性一般只涉及1级连接和2级连接(图5-13),但对于一些超高功率密度、需要在芯片内部实施微纳尺度冷却通道的芯片还需要考虑0级连接。

图5-13 典型PBGA封装元器件的一级连接和二级连接

在分别分析各类常见封装形式的热特性之前,我们先对典型芯片的内部组成物质(可以参考图5-13)进行定性的热分析:

1)芯片结(或晶圆,die):硅或砷化镓材料,芯片内部主要发热源,导热系数 ~102W/m.K;

2)粘结剂 (Die Attach):将die固定到焊盘上的中间介质,导热系数较低,可以添加高导热填料(银)增加导热系数,导电银浆就是一种常用的粘接剂。粘接剂的导热系数~100 W/m.K;

3)芯片焊盘(Die Pad):一般是铜材,有热扩展和机械固定的作用,导热系数 ~102W/m.K;

4)键合线(Bond Wire):金或铝制,数目等同于外面管脚数,信号传输、热量传输,有些封装形式中芯片没有键合线(如FC-BGA封装)。导热系数 ~102W/m.K;

5)基板(Substrate):类似于小尺寸的单板,有些芯片没有基板。与单板类似,基板的导热系数是各项异性的,水平方向~101W/m.K,厚度方向~10-1W/m.K(单板的相关热特性会在本章第六节详细阐述);

6)引脚(Lead frame):铜金或铝制,和内部的键合线一一对应,信号传输,热量传输,有些芯片没有引脚(图5-13中的PBGA封装就没有引脚,元器件与单板之间的连接通过焊球实现)。导热系数 ~102W/m.K;

7)焊球(Solder ball):通常材料为锡铅合金95Pb/5Sn或37Pb/63Sn,有些芯片没有焊球(如图5-9所示的两种封装形式,元器件与单板之间的连接通过引脚实现)。导热系数~101 W/m.K;

8)密封材料(Encapsulant):有金属、陶瓷、塑料三种,塑料最为常用,外围的、保护晶圆的材质,有些芯片(如裸die封装的芯片)没有密封材料。密封材料的导热系数和材料类型紧密相关,塑料封装导热系数~10-1W/m.K,金属或陶瓷封装则可高达数十甚至上百W/m.K。

注:上述各个组成部分的材料参数参考的是典型元器件中可能出现的物质。部分特殊的封装,材料类型及性质可能会有变化。

建立了芯片各组成部分的导热系数量级概念之后,再来审视不同封装形式元器件的热特性就变得简单了。当前常见的元器件封装形式及其热特性列示如下:

5.1 BGA—Ball Grid Array Package 球栅阵列式封装

BGA封装是当前高集成度芯片最常用的封装,几乎所有高端IC均在使用这一封装。BGA封装的最显著特征是其二级连接是以圆形或柱状焊点按阵列形式分布在封装晶圆下面,并且以二维分布的形式阵列开来。

根据晶圆外围封装材料和基板材质的不同,BGA封装又分为如下三种:

塑料球形封装(Plastic Ball Grid Array Package,图5-13):晶圆外围包覆材料为塑料,基板为常见FR4基板,由于塑料导热系数低,热阻相对较高;

陶瓷球形封装(Ceramic Ball Grid Array Package):使用陶瓷基板,结板热阻相对较低;

裸die封装(图5-14):晶圆外围不再包覆材料,而是直接裸 露在外,结壳热阻极低。

图5-14 典型裸die封装各组成部分

BGA封装与单板之间的连接点是二维的形式,连接面更广,从热的角度上讲,相当于传热面积更大,因此结板热阻相对也低。另外,结到单板上的热阻可以通过在基板上施加热过孔,在基板底侧正对芯片结之处亦可施加铜片来进行降低。裸die封装的BGA芯片,芯片结直接暴露在外,最大程度降低了结壳热阻。

5.2 TO——Transistor Outline Package晶体管外形封装

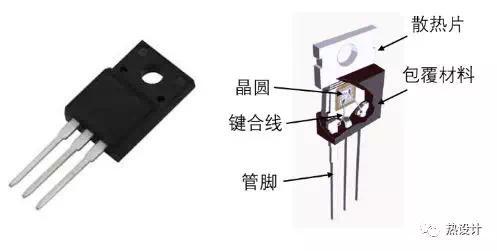

TO封装是较早期的封装形式,多用在电源开关芯片。从热特性角度上分析,TO封装的元器件有如下特征:

1) 插针接触单板,插针与芯片结通过键合线连接,热量传递有限,通过单板的散热阻力较大;

2) 芯片结外层往往包裹塑胶材料,故塑胶侧热阻较高;

3) 金属侧热阻较低,是主要的传热路径;

4) TO封装的结板热阻非常难定义,或者说,其值受工况影响较大。

图5-15 TO封装元器件示意图

5.3 QFP---- Quad Flat Pack 四边扁平封装

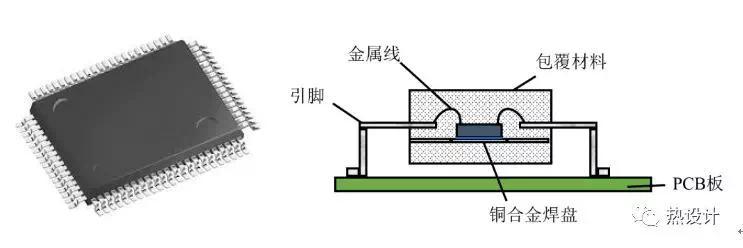

四边扁平封装的元器件,其二级连接是一维分布,即只分布在芯片四边。四周管脚通过键合线与内部晶圆进行一一对应连接,管脚另一侧连接到单板上。

图5-16 QFP封装外形示意及典型内部结构和材料分布简图

从热特性角度分析,QFP封装的元器件有如下特征:

1)热阻高,引脚成为传热的重要途径(一般仍<15%) ;

2)多数QFP芯片底部不与单板接触,底部加热过孔收效甚微。特殊情况下可以在底部施加界面材料,连通芯片底壳和单板,降低结板热阻;

3)顶部由于大多采用塑料封装,结壳热阻也比较大;

4)内部铜合金焊盘有助于在包覆材料内部均热;

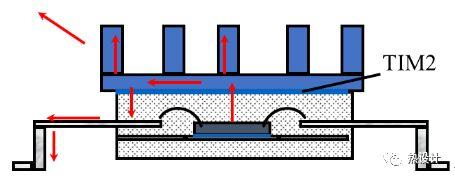

5)塑料包覆材料导热系数,当晶圆相对封装尺寸较小时,芯片正顶部温度较高,金属散热片均热效果好,可能导致热量回流,致使管脚温度变高。当管脚温度是芯片热可靠性控制参数时,应当注意热量的引流方向(如应加高而不是加长、加宽散热器)。

图5-17 QFP封装芯片的热量回流现象(红色箭头表示热量流动路径)

5.4 QFN/DFN ---- (Quad/DualFlat No-Lead)四边/双边无引脚扁平封装

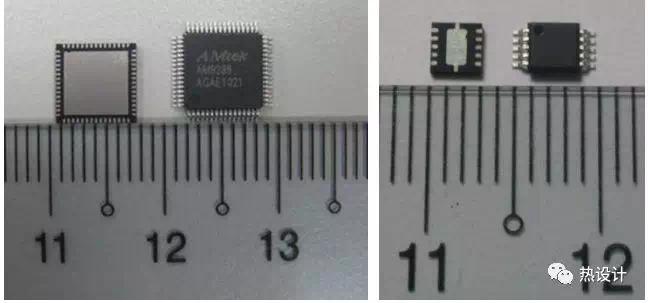

QFN和DFN是由QFP封装演变而来。其最大区别是将四边管脚收至芯片内部,使得芯片封装体积大大缩减。

图5-18 QFN/DFN和QFP/DFP封装芯片尺寸对比(管脚数相同)

QFN的基本热特性如下:

1)QFN中die所占封装的比例往往很大,故Rjc和Rjb都较小;

2) 主要传热路径:Die à焊盘à裸焊盘 à PCB;

3) 次要传热路径:Lead;

4) QFN芯片底部一般直触PCB地层,因此芯片板下添加热过孔可以有效加强散热。

图5-19 QFN芯片内部结构及其单板之间的连接示意图

5.5 封装演变趋势和热设计面临的机遇与挑战

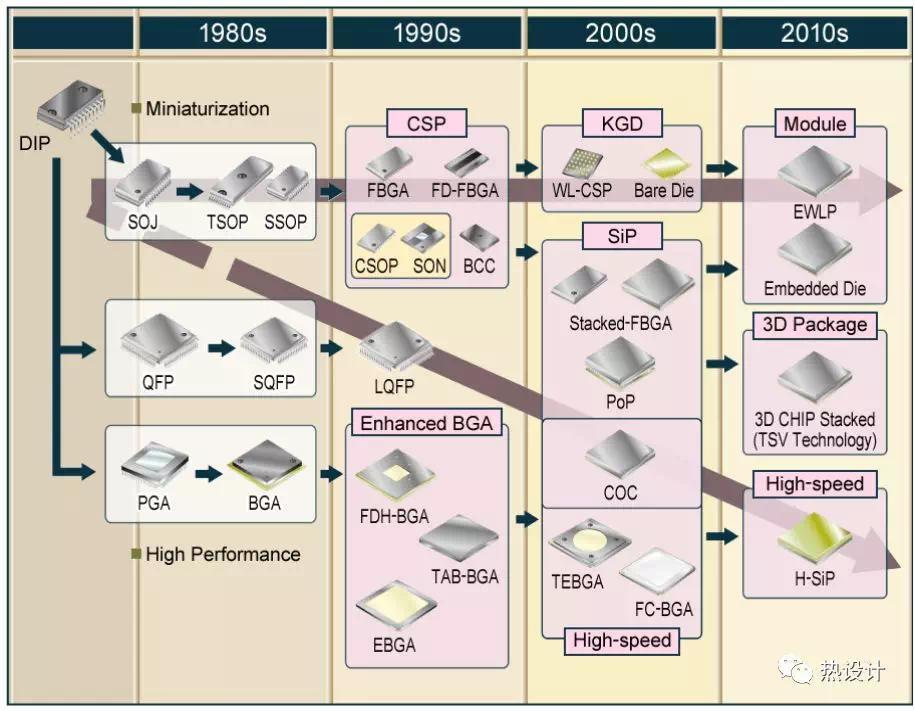

体积是目前所有电子设备面临的共同需求。所有的产品经理都希望在尽可能小的设备上实现尽可能强大的功能,这一需求促使着所有相关的行业飞速进步。元器件的封装也是如此。在尽可能小的空间内挤入更多晶体管,并使用封装技术保证芯片的可靠性正变得越来越难。下图描述了1980年~2010年件芯片封装形式的演进,可以清楚看到单板和芯片之间的连接正从管脚连接演变为晶圆底部焊球连接,并且人们正不断尝试提高晶圆所占比例,90年代就出现了芯片级封装(Chip Scale Package,封装相对于Die尺寸不大于20%)。从芯片设计层面,人们开发出了SOC(System on a Chip),而从封装技术角度出发,人们一直在努力实现SIP(System in a Package)。对空间的持续追求和半导体制程的发展速度限制还促使人们开发出了3D封装,及芯片堆叠甚至晶圆级堆叠。

图5-20 芯片封装趋势图

芯片封装集成度的提升为产品散热设计带来了前所未有的挑战。虽然架构的优化设计可以提高芯片的能效比,但晶体管的增多带来的发热量提升仍然导致元器件平均功耗逐年攀升。另外,由于封装精度要求不断提升,芯片对温度变化带来的力、电效应也越来越敏感。随着半导体制程濒临物理极限,热科学可能成为半导体行业进步的核心技术。

参考文献:

[1] Sergio Lopez-Buedo, Eduardo Boemo. Electronic Packaging Technologies.

[2] Trends in Package Development. http://www.fujitsu.com/downloads/MICRO/fma/pdf/a810000114e.pdf

作者简介:陈继良,仿真秀专栏作者,文章节选自机械工业出版社发行,陈继良老师编著的《从零开始学散热》,点击可订购。